#### DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

**COURSE: LINEAR IC APPLICATIONS**

**BRANCH**: Eletronics and communication Engineering

CLASS: II/II Sem.

**YEAR:** 2022-23

# LECTURE NOTES

your roots to success...

### **NARSIMHA REDDY**

NARSIMHA REDDY ENGINEERING COLLGE,

MAISAMMAGUDA, HYDERABAD - 500100

### **INDEX**

| S. NO. | CONTENT                                  | PAGE NO. |

|--------|------------------------------------------|----------|

| 1      | UNIT I: INTEGRATED CIRCUITS              | 3 - 12   |

| 2      | UNIT II: APPLICATIONS OF OP-<br>AMPS     | 13 - 57  |

| 3      | UNIT III: ACTIVE FILTERS AND OSCILLATORS | 58 - 78  |

| 4      | UNIT IV: TIMERS AND PHASE LOCKED LOOPS   | 79–85    |

| 5      | UNIT V: A-D AND D-A<br>CONVERTERS        | 86 – 105 |

your roots to success..

# UNIT I INTEGRATED CIRCUITS

your roots to success...

#### INTEGRATED CIRCUITS

An integrated circuit (IC) is a miniature, low cost electronic circuit consisting of active and passive components fabricated together on a single crystal of silicon. The active components are transistors and diodes and passive components are resistors and capacitors.

#### Advantages of integrated circuits

- 1. Miniaturization and hence increased equipment density.

- 2. Cost reduction due to batch processing.

- 3. Increased system reliability due to the elimination of soldered joints.

- 4. Improved functional performance.

- 5. Matched devices.

- 6. Increased operating speeds.

- 7. Reduction in power consumption

Depending upon the number of active devices per chip, there are different levels of integration

|    | Level of integration                 | Number of active devices per chip |  |  |

|----|--------------------------------------|-----------------------------------|--|--|

| 1. | Small scale integration (SSI)        | Less than 100                     |  |  |

| 2. | Medium scale integration (MSI)       | 100 - 10000                       |  |  |

| 3. | Large scale integration (LSI)        | 1000 - 100,000                    |  |  |

| 4. | Very large scale integration (VLSI)  | Over 100,000                      |  |  |

| 5. | Ultra large scale integration (ULSI) | Over 1 million -                  |  |  |

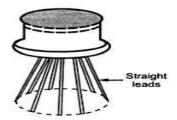

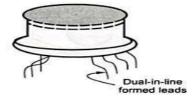

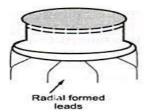

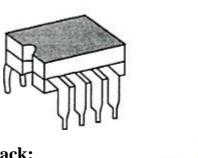

### IC Package Types 11 10015 10 SUCCESS...

The op-amp ICs are available in various packages. The IC packages are classified as,

- 1. Metal Can

- 2. Dual In Line

- 3. Flat Pack

#### **Metal Can package:**

#### **Dual-in-Line Package:**

**Flat Pack:**

10 lead version

#### **DIFFERENTIAL AMPLIFIER:**

The differential amplifier consists of two symmetrical common-emitter sections and is capable of amplifying the difference between two input signals. The differential amplifier can amplify ac as well as dc input signals because it employs direct coupling.

There are four types of differential amplifier configurations:

(a) The dual Input, Balanced output differential amplifier

DC Analysis -----

$$I_E = V_{EE} - V_{BE}/2R_E$$

,

AC Analysis-----

$$A_d=R_C/r_e$$

$$R_{i1} = R_{i2} = 2\beta_{ac}r_e$$

$$R_{01}=R_{02}=R_{c}$$

(b) The dual input, unbalanced output differential Amplifier

DC Analysis -----

$$I_E\!=\!V_{EE}$$

-  $V_{BE}/(2R_E\!+\!R_{in}\!/\!\beta_{dc})$

AC Analysis-----

$$A_d=R_C/2r_e$$

$$R_{i1} = R_{i2} = 2\beta_{ac}r_e$$

$$R_0 = R_c$$

(c) The single input, balanced output differential Amplifier

DC Analysis -----

$$I_E\!=\!\!V_{EE}$$

-  $V_{BE}\!/(2R_E\!\!+\!\!R_{in}\!/\beta_{dc})$

$$V_{CE}=V_{CC}+V_{BE}-R_cI_{CO}$$

AC Analysis -----

$$I_E = V_{EE} - V_{BE}/(2R_E + R_{in}/\beta_{dc})$$

$$R_i=2\beta_{ac}r_e$$

$$R_{01}=R_{02}=R_c$$

(d) The single input, unbalanced output differential Amplifier

DC Analysis -----

$$I_E = V_{EE} - V_{BE}/(2R_E + R_{in}/\beta_{dc})$$

$$V_{CE}=V_{CC}+V_{BE}-R_cI_{CQ}$$

$$R_{i=}2\beta_{ac}r_{e}$$

$$R_0 =$$

$R_{c} \\$

| Configuration                      | Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | A <sub>d</sub> voltage<br>gain                                      | R <sub>in</sub> Input<br>Resistance  | R <sub>o</sub> Output<br>Resistance |

|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|--------------------------------------|-------------------------------------|

| Dual Input<br>Balanced Output      | R <sub>C</sub> R <sub>C</sub> R <sub>C</sub> R <sub>S2</sub> R <sub>S2</sub> V <sub>S</sub> | h <sub>fe</sub> R <sub>C</sub><br>R <sub>S</sub> + h <sub>ie</sub>  | $2(R_S + h_{ic})$                    | Rc                                  |

| Dual Input<br>Unbalanced<br>Output | R <sub>C</sub> V <sub>o</sub> R <sub>C</sub> V <sub>s2</sub> V <sub>s3</sub> V <sub>s</sub> | h <sub>fe</sub> R <sub>C</sub> 2(R <sub>S</sub> + h <sub>ie</sub> ) | 2(R <sub>S</sub> + h <sub>ic</sub> ) | R <sub>C</sub> ·                    |

| Single Input<br>Balanced Output      | R <sub>C</sub> R <sub>E</sub> | h <sub>fe</sub> R <sub>C</sub><br>R <sub>S</sub> + h <sub>ie</sub>    | 2(R <sub>S</sub> + h <sub>ic</sub> ) | R <sub>C</sub> |

|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|--------------------------------------|----------------|

| Single Input<br>Unbalanced<br>Output | R <sub>C</sub>                                                                                                          | $\frac{h_{\text{fe}} R_{\text{C}}}{2 (R_{\text{S}} + h_{\text{ie}})}$ | 2(R <sub>S</sub> + h <sub>ic</sub> ) | R <sub>C</sub> |

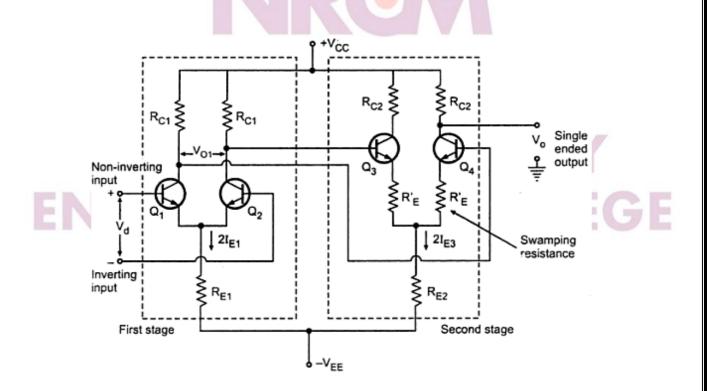

#### **Cascade Differential Amplifier Stages:**

In cascaded differential amplifier, the output of the first stage is used as an input for the second stage, the output of the second stage is applied as an input to the third stage, and so on. Because of direct coupling between the stages, the operating point of succeeding stages changes

The 741C Op Amp is connected in Inverting mode having following parameters Given:  $V_{in}$  = 0.6V,  $R_F$  = 20 K $\Omega$  ,  $R_1$  = 2 K $\Omega$  ,  $A_{OL}$  = 400k ,  $R_{in}$  = 8 M $\Omega$  ,  $R_o$  = 60  $\Omega$

Find:  $V_0$ ,  $i_F$ ,  $A_v$ ,  $\beta$ ,  $R_{inF}$  and

#### RoF Solution:

$$\mathbf{V_0} = (-\frac{R_f}{R_1}) \, \mathbf{V_{in}} = (-\frac{20}{2}) \, \mathbf{x} \, 0.6 = -6 \, \mathbf{Volt}$$

$$I_F = \frac{V_{in}}{R_1} = \frac{0.6}{2000}$$

0.3 mA

(Also,

$$I_f = \frac{V_o - V_f}{R_f} = \frac{6 - 0}{20000} = \frac{6}{20000} = 0.3 \text{ mA}$$

) as  $V_F$  is virtual ground

$$\mathbf{A_v} = \left(-\frac{R_f}{R_1}\right) = \left(-\frac{20}{2}\right) = \mathbf{10}$$

$$\beta = \frac{R_1}{R_1 + R_f} = \frac{2}{2 + 20} 0.0909$$

$$\mathbf{R_{inF}} = \mathbf{R_1} = 2000 \,\mathbf{\Omega}$$

$$\mathbf{R}_{oF} = \frac{R_o}{1 + \beta A_{oL}}$$

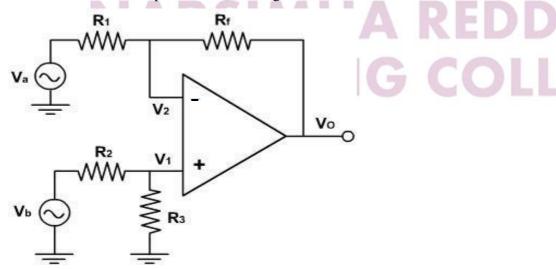

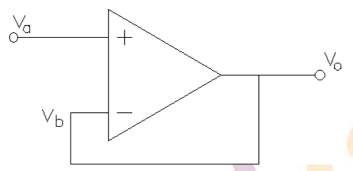

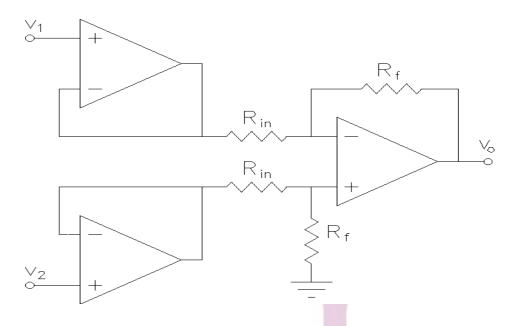

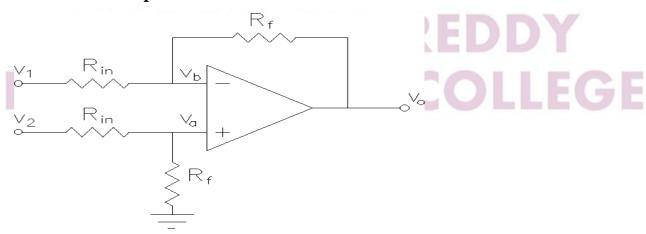

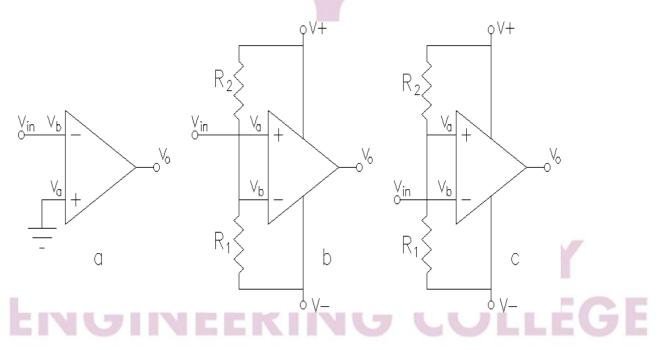

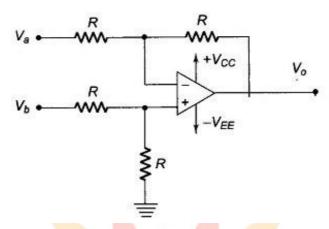

Draw the circuit of differential amplifier using one Op. Amp. and derive the equation of differential gain  $(A_D)$ .

The differential amplifiers amplify the difference between two input voltages makingthis type of operational amplifier circuit a Subtractor.

The basic differential amplifier is shown in figure

Since there are two inputs Superposition theorem can be used to find the outputvoltage.

When,  $V_b = 0$ ,

then the circuit becomes inverting amplifier, hence the output is due to  $V_a$  only.

Similarly

$$V_{oa} = -\frac{R_f}{R_1} V_{a}$$

---- (1)

When,  $V_a = 0$ ,

the configuration is a Non-inverting amplifier having a voltage divided networkat the noninverting input.

$$V_{ob} = (1 + \frac{R_f}{R_1}) V_1$$

---- (2)

but in equation (2)

$$V_{ob} = (1 + \frac{R_f}{R_1}) V_1 - \dots (2)$$

$$V_1 = (\frac{R_2}{R_2 + R_3}) V_a - \dots (3)$$

Substituting the value of  $V_1$ , in equation (2)

$$V_{\text{ob}} = (1 + \frac{R_f}{R_1}) (\frac{R_f}{R_2 + R_3}) V_{\text{a}} ----- (4)$$

In equation (4) if  $R_2 = R_1$  and  $R_3 = R_f$  then equation (4) can be written as

$$V_{ob} = (\frac{R_f}{R_1}) V_{a} - - - (6)$$

As per Superposition theorem sum of equation (1) and (6) is total output voltage.

$$V_{0} = (-\frac{R_{f}}{R_{1}})(V_{a} - V_{b}) ---- (7)$$

Now, differential Gain can be written as

$$A_{D} = \frac{V_{o}}{V_{ab}} = \frac{V_{o}}{V_{a}-V_{b}} = -\frac{R_{f}}{R_{1}} - \dots (8)$$

your roots to success...

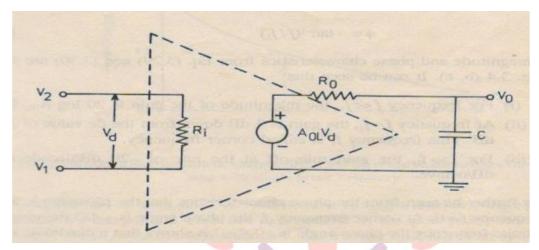

#### 2.1 Ideal OP-AMP

An ideal OP-AMP would have the following characteristics:

- 1. The input resistance R<sub>IN</sub> would be infinite

- 2. The output resistance R<sub>OUT</sub> would be zero

- 3. The voltage gain, V<sub>G</sub> would be infinite

- 4. The bandwidth (how quickly the output will follow the input) would be infinite

- 5. If the voltages on the two inputs are equal than the output voltage is zero ( If the output is not zero it is said to have an offset)

#### 2.2. Block diagram of op-amp:

The block diagram of IC op-amp is as shown in figure

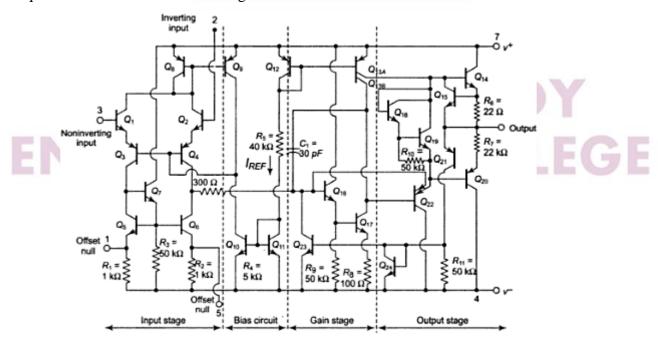

#### **Op-amp 741:**

The IC 741 is high performance monolithic op-amp IC .It is available in 8 pin, 10 pin or 14 pin configuration. It can operate over a temperature of -55 to 125 centigrade.op-amp 741 equivalent circuit is as shown in figure.

#### **Features of IC-741**

- i. No frequency compensation required.

- ii. Short circuit protection provided.

- iii. Offset voltage null capability.

- iv. Large common mode and Differential voltage range.

- v. No latch up.

#### **PSRR:**

PSRR is Power Supply Rejection Ratio. It is defined as the change in the input offset voltage due to the change in one of the two supply voltages when other voltage is maintained constant. It's ideal value should be Zero.

#### **Slew Rate:**

The maximum rate of change of output voltage with respect to time is called Slew rate of the Op-amp.

It is expressed as,  $S = \frac{1}{2}$  and measured in V/sec.

The Slew rate equation is,  $S = 2\pi f V_m V/sec$

#### Frequency compensation technique:

In application where one desires large bandwidth and lower closed loop gain, suitable compensation technique are used: Two types of compensation techniques are used

1. External compensation

# 2. Internal compensation ENGLISHER COLLEGE

your roots to success...

#### **OPERATION AMPLIFIER**

An operational amplifier is a direct coupled high gain amplifier consisting of one or more differential amplifiers, followed by a level translator and an output stage. It is a versatile device that can be used to amplify ac as well as dc input signals & designed for computing mathematical functions such as addition, subtraction ,multiplication, integration & differentiation

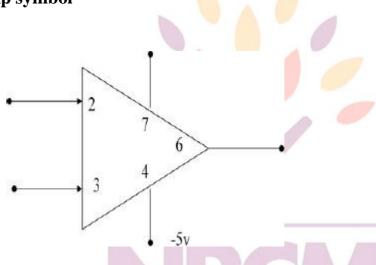

#### **Op-amp symbol**

#### **Ideal characteristics of OPAMP**

- 1. Open loop gain infinite

- 2. Input impedance infinite

- 3. Output impedance low

- 4. Bandwidth infinite

- 5. Zero offset, ie, Vo=0 when V1=V2=0

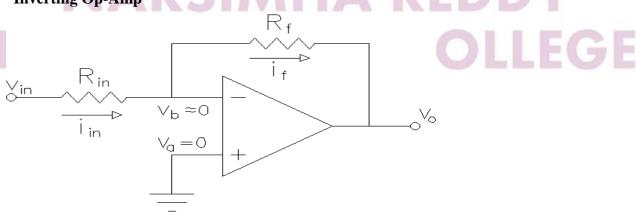

#### **Inverting Op-Amp**

$$V_{OUT} = -V_{IN} \frac{R_f}{R_1}$$

#### Voltage follower

$$V_{\scriptscriptstyle OUT} = V_{\scriptscriptstyle IN}$$

#### **DC** characteristics

#### **Input offset current**

The difference between the bias currents at the input terminals of the op- amp is called as input offset current. The input terminals conduct a small value of dc current to bias the input transistors. Since the input transistors cannot be made identical, there exists a difference in bias currents

#### Input offset voltage

A small voltage applied to the input terminals to make the output voltage as zero when the two input terminals are grounded is called input offset voltage

### Input bias current

Input bias current IB as the average value of the base currents entering into terminal of an opamp

$$I_B = I_B^+ + I_B^-$$

#### **AC** characteristics

#### **Frequency Response**

HIGH FREQUENCY MODEL OF OPAMP

#### **Need for frequency compensation in practical op-amps**

- Frequency compensation is needed when large bandwidth and lower closed loop gain is desired.

- Compensating networks are used to control the phase shift and hence to improve the stability

#### Frequency compensation methods

- Dominant- pole compensation

- Pole- zero compensation

#### Slew Rate

- The slew rate is defined as the maximum rate of change of output voltage caused by a step input voltage.

- An ideal slew rate is infinite which means that op-amp's output voltage should change instantaneously in response to input step voltage

#### **Instrumentation Amplifier**

In a number of industrial and consumer applications, the measurement of physical quantities

is usually done with the help of transducers. The output of transducer has to be amplified So that it can drive the indicator or display system. This function is performed by an instrumentation amplifier

#### Features of instrumentation amplifier

- 1. high gain accuracy

- 2. high CMRR

- 3. high gain stability with low temperature co- efficient

- 4. low dc offset

- 5. low output impedance

#### Differentiator

The circuit which produces the differentiation of the input voltage at its output is called differentiator. The differentiator circuit which does not use any active device is called passive differentiator. While the differentiator using an active device like op-amp is called an active differentiator.

#### **Integrator:**

This circuit amplifies only the difference between the two inputs. In this circuit there are two

resistors labeled R IN Which means that their values are equal. The differential amplifier amplifies the difference of two inputs while the differentiator amplifies the slope of an input

#### **Summer:**

#### **Comparator:**

A comparator is a circuit which compares a signal voltage applied at one input of an op- amp with a known reference voltage at the other input. It is an open loop op - amp with output.

#### **Applications of comparator:**

- 1. Zero crossing detector

- 2. Window detector

- 3. Time marker generator

- 4. Phase detector

#### 3.15 Triangular wave Generator:

The output of the integrator is triangular if the input is a square wave. This means that a triangular wave generator can be formed by simply connecting an integrator to the square wave generator.

#### 3.17 Square wave generator:

Square wave outputs are generated when the op-amp is forced to operate in the saturated region. That is, the output of the op-amp is forced to swing repetitively between positive saturation and negative saturation. The square wave generator is also called as free-running or Astable mutivibrator

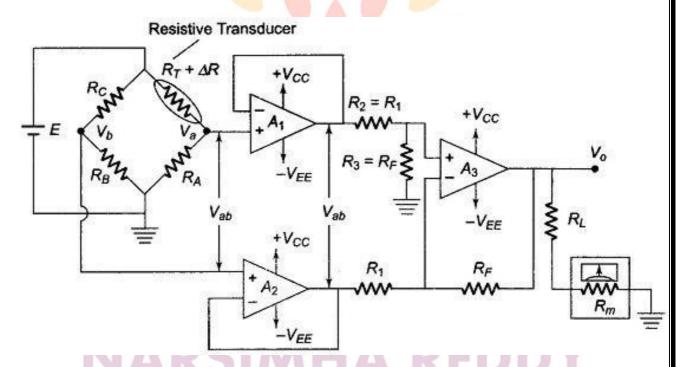

#### **Explain Instrumentation Amplifier in detail. OR**

Draw and explain the circuit diagram of Instrumentation Amplifier using transducer bridge which is consisting of Thermistor in one of it's arm of bridge. OR

#### **Explain differential Instrumentation Amplifier with transducer bridge**

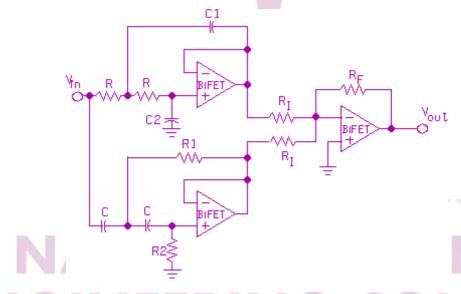

Simplified circuit of a Differential Instrumentation Amplifier with Transducer Bridge is as shown in figure.

In this circuit a resistive transducer/Thermistor (whose resistance changes as a function of some physical energy/Temperature) is connected to one arm of the bridge.

Let  $R_T$  be the resistance of the transducer and  $\Delta R$  the change in resistance of the resistive transducer. Hence the total resistance of the transducer is  $(R_T \pm \Delta R)$ .

The condition for bridge balance is  $V_b = V_a$ , i.e. the bridge is balanced when  $V_b = V_a$ , or when,

$$\frac{R_B(E)}{R_B + R_C} = \frac{R_A(E)}{R_A + R_T}$$

Therefore,

$$\frac{R_c}{R_B} = \frac{R_T}{R_A}$$

The bridge is balanced at a desired *reference condition*, which depends on the specific value of the physical quantity to be measured. Under this condition, resistors  $R_A$ ,  $R_B$  and  $R_C$  are so selected that they are equal in value to the transducer resistance  $R_T$ . (The value of the physical quantity normally depends on the transducers characteristics, the type of physical quantity to be measured, and the desired applications.)

Initially the bridge is balanced at a desired reference condition. As the physical quantity to be measured changes, the resistance of the transducer also changes, causing the bridge to be unbalanced ( $V_b \neq V_a$ ). Hence, the output voltage of the bridge is a function of the change in the resistance of the transducer. The expression for the output voltage  $V_0$ , in terms of the change in resistance of the transducer is calculated as follows.

Let the change in the resistance of the transducer be  $\Delta R$ . Since  $R_B$  and  $R_C$  are fixed resistors, the voltage  $V_b$  is constant, however, the voltage  $V_a$  changes as a function of the change in the transducers resistance.

Therefore, applying the voltage divider rule we have

$$V_a = \frac{R_A(E)}{R_A + (R_T + \Delta R)}$$

and  $V_b = \frac{R_B(E)}{R_B + R_C}$

your roots to success...

The output voltage across the bridge terminal is  $V_{ab}$ , given by  $V_{ab}=V_a-V_b$ Therefore,

$$V_{ab} = \frac{R_A(E)}{R_A + (R_T + \Delta R)} - \frac{R_B(E)}{R_B + R_C}$$

$$R_A = R_B = R_C = R_T = R, \text{ then}$$

$$V_{ab} = \frac{R(E)}{2R + \Delta R} - \frac{R(E)}{2R} = E\left(\frac{R}{2R + \Delta R} - \frac{1}{2}\right)$$

$$V_{ab} = E\left(\frac{2R - 2R - \Delta R}{2(2R + \Delta R)}\right) = \frac{-\Delta R(E)}{2(2R + \Delta R)}$$

The output voltage  $V_{ab}$  of the bridge is applied to the Differential Instrumentation Amplifier through the voltage followers to eliminate the loading effect of the bridge circuit. The gain of the basic amplifier is  $(R_F/R_1)$  and therefore the output voltage  $V_0$  of the circuit is given by

$$V_o = V_{ab} \left( \frac{R_F}{R_1} \right) = \frac{-\Delta R(E)}{2(2R + \Delta R)} \times \frac{R_F}{R_1}$$

It can be seen from the above equation that  $V_o$  is a function of the change in resistance  $\Delta R$  of the transducer. Since the change is caused by the change in a physical quantity, a meter connected at the output can be calibrated in terms of the units of the physical quantity.

#### Applications of Instrumentation Amplifier with Transducer Bridge

We shall now consider some important applications of instrumentation amplifiers using resistance types transducers. In these transducers, the resistance of the transducer changes as a function of some physical quantity. Commonly used resistance transducers are thermisistors, photoconductor cells, and strain gauges.

- (i) Temperature Indicators Using Thermistor

- (ii) Light Intensity Meter

- (iii) Analog Weight Scale

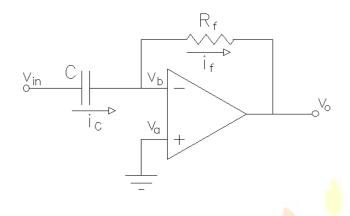

#### Explain Integrator circuit in detail. OR

Draw circuit diagram of Integrator using Op. Amp. and derive the equation of output voltage. Also draw the output waveform if input is (i) Sine wave and (ii) Square wave. OR

Draw circuit diagram of Integrator using Op. Amp and explain it with necessary frequency response and derivations. Also draw practical Integrator circuit.

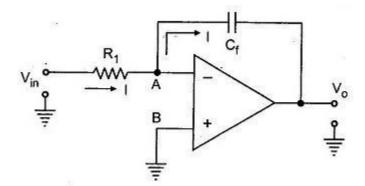

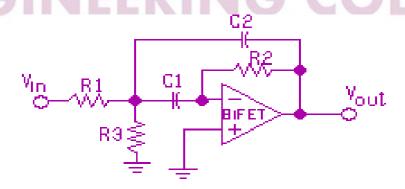

An integrator is the circuit in which the output voltage waveform is the integral of the input voltage waveform. It can be obtained by replacing feedback resistor by *feedback capacitor* in basic inverting amplifier. Input signal, which can be applied at the inverting terminal i.e. pin - 2 of the op-amp through resistor Rin. A feedback capacitor Cf is connected between the output terminal i.e. pin - 6 and the inverting terminal i.e. pin - 2 of the op-amp.

The non-inverting terminal i.e. pin - 3 of the op-amp is grounded either directly or through a resistor which is a parallel combination of input resistor Rin and feedback resistor Rf. Figure 1 shows Basic Integrator Circuit.

The output of the op-amp will then be integrated version of the input.

#### **DESIGN EQUATION:**

Applying KCL at inverting node,

$$Iin = IB + IF$$

As input impedance of op-amp is very large, bias current IB =0. Therefore,

$$Iin = IF = I$$

The current through resistor R<sub>1</sub> can be given as

$$I = \frac{V_{in} - V_A}{R_1} = \frac{V_{in}}{R_1}$$

----(1)

The current through capacitor can be given as

$$I = C_f \frac{d(V_A - V_o)}{dt}$$

$$I = -C_f \frac{dV_o}{dt}$$

$$I = -C_f \frac{dV_o}{dt}$$

Because of virtual ground concept VA=VB=0 in equation (1) and (2).

#### Now comparing equation (1) and (2)

$$\frac{V_{in}}{R_1} = -C_f \frac{dV_o}{dt}$$

----(3)

Integrating both sides of equation (3)

$$\int_{0}^{t} \frac{V_{in}}{R_{1}} dt = -C_{f} \int \frac{dV_{o}}{dt} . dt$$

i.e.

$$\int_{0}^{t} \frac{V_{in}}{R_{1}} dt = -C_{f} V_{o}$$

$$--- (4)$$

$$V_{o} = -\frac{1}{R_{1} C_{f}} \int_{0}^{t} V_{in} dt + V_{o}(0)$$

$$V_{o} = -\frac{1}{R_{1} C_{f}} \int_{0}^{t} V_{in} dt \qquad --- (5)$$

Equation (5) indicates that output is integration of input voltage. Hence this circuit willwork as an integrator circuit.

Where  $V_0(0)$  is constant of integration and it indicates initial value of output voltage at time t=0.

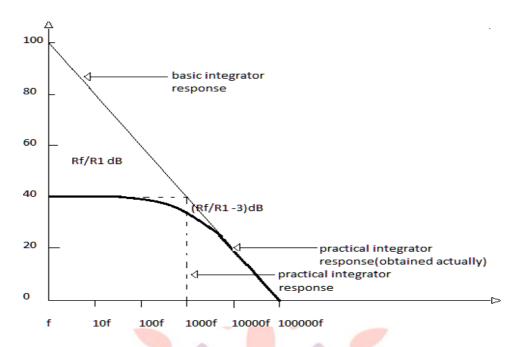

#### **Frequency Response of Integrator:**

Frequency response is graph relating Gain and Frequency.

Capacitive reactance  $\mathbf{X}\mathbf{c} = \frac{1}{2\pi\mathbf{f}\mathbf{C}}$

As frequency is increases, Xc and gain will decreases.

But at low frequency capacitive reactance Xc is high, so gain is very large and circuit becomes unstable at low frequency input signal. To control the gain at low frequency, a Resistor Rf is required to be connected in parallel with Cf in practical integrator circuit. Frequency response of Ideal/Basic integrator and practical integrator circuit is as shown in figure.

Frequency Response of Basic & Practical Integrator

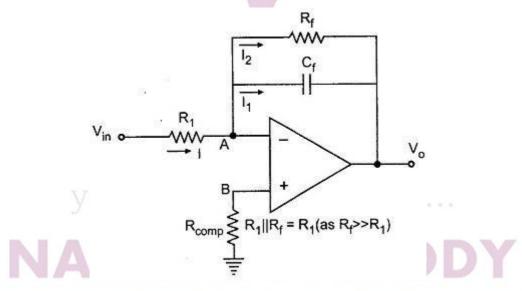

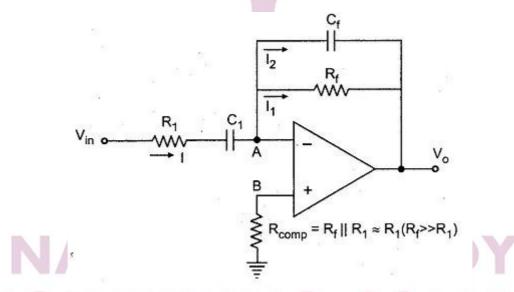

PRACTICAL INTEGRATOR CIRCUIT:

### Practical Integrator circuit DESIGN:

Frequency at which gain starts decreases is called gain limiting frequency and is given by equation

$f_a = \frac{1}{2\Pi R_f C_f}$ The frequency at which the gain is 0 dB (Unity) is given by equation

$$f_b = \frac{1}{2\Pi R_1 C_f}$$

Generally  $f_b = 20 f_a$

Now selecting standard value of capacitor Cf we can determine the value of R1 and Rfusing equation of  $\mathbf{f_a}$  and  $\mathbf{f_b}$  to design Integrator of particular frequency range.

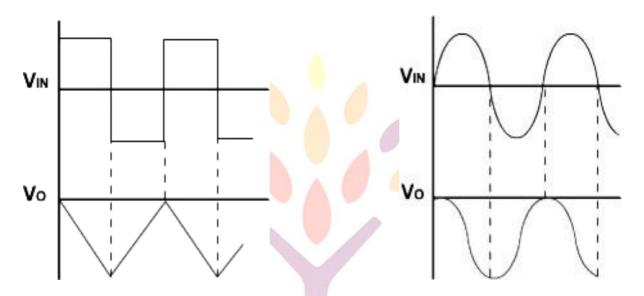

#### **INPUT & OUTPUT WAVE FORMS: -**

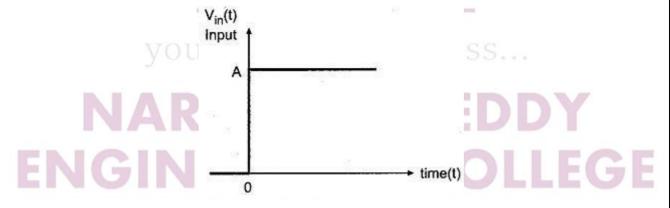

Draw the output wave form if unit step input is applied to an integrator as shown in figure.

Let the input waveform is of step type, with a magnitude of A units as shown in the figure.

For simplicity of understanding, assume that the time constant  $R_1C_f = 1$  and the initial voltage  $V_0(0) = OV$ .

Mathematically the step input can be expressed as,

$$V_{in}(t) = A \text{ for } t \ge 0$$

$$= 0 \text{ for } t < 0$$

From above equation with  $R_IC_f = 1$  and  $V_0(0) = 0$ ,

$$V_{o}(t) = -\int_{0}^{t} V_{in}(t) dt = -\int_{0}^{t} A dt = -A \int_{0}^{t} dt = -A [t]_{o}^{t}$$

$$V_{o}(t) = -At$$

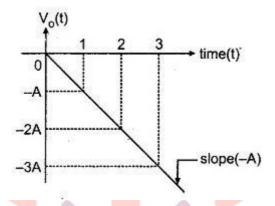

Now the output waveform can be drawn as follow:

Thus output waveform is a straight line (negative going Ramp) with a slope of -A where A is magnitude of the step input. The output waveform is shown in the figure.

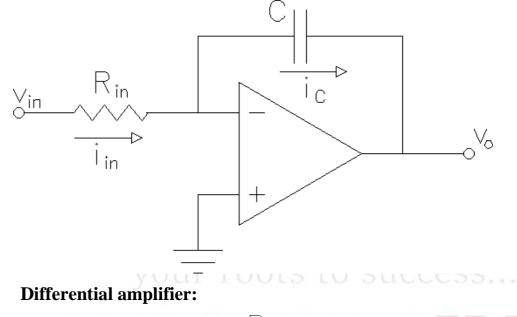

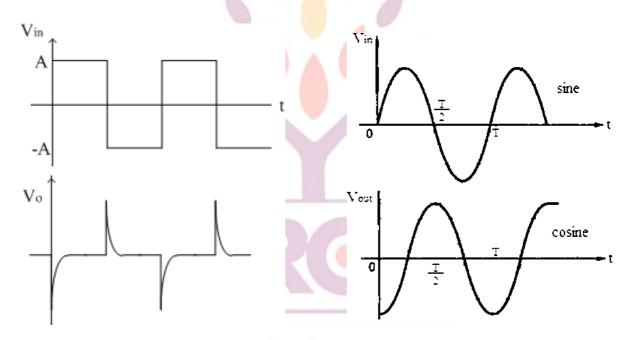

#### Explain Differentiator circuit in detail. OR

Draw circuit diagram of Differentiator using Op. Amp. and derive the equation of output voltage. Also draw the output waveform if input is (i) Sine wave, (ii) Square wave and (iii) Triangular wave. OR

Draw circuit diagram of Differentiator using Op. Amp and explain it with necessary frequency response and derivations. Also draw practical Differentiator circuit.

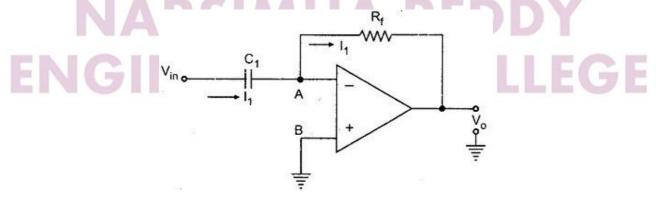

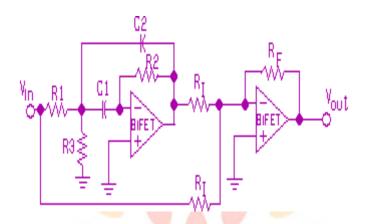

The circuit which produces the differentiation of the input voltage at its output is called *Differentiator*. The differentiator using an active device like op-amp is called an active Differentiator. Let us discuss first the operation of Ideal/Basic Differentiator circuit.

The active differentiator circuit can be obtained by exchanging the positions of R and C in the basic integrator circuit. The op-amp differentiator circuit is shown in the figure.

The node B is grounded. The node A is also at the ground potential because of virtual ground, hence  $V_A = 0$ .

#### **DESIGN EQUATION: -**

Applying KCL at inverting node,

$$I_{in} = I_B + I_F$$

As input impedance of op-amp is very large, bias current I<sub>B</sub> =0. Therefore,

$$I_{in} = I_F = I_1$$

The current through capacitor C<sub>1</sub> can be given as

$$I_1 = C_1 \frac{d(V_{in} - V_A)}{dt} = C_1 \frac{dV_{in}}{dt}$$

The current through resistor R<sub>f</sub> can be given as

$$I = \frac{(V_A - V_o)}{R_f} = -\frac{V_o}{R_f}$$

----(2)

Because of virtual ground concept  $V_A=V_B=0$  in equation (1) and (2).

Now comparing equation (1) and (2)

$$C_1 \frac{d V_{in}}{dt} = -\frac{V_o}{R_f}$$

Hence,

$$V_0 = -C_1 \cdot R_f \cdot \frac{d V_{in}}{dt}$$

(4)

Equation (4) indicates that output is differentiation of input voltage. Hence this circuitwill work as an differentiator circuit.

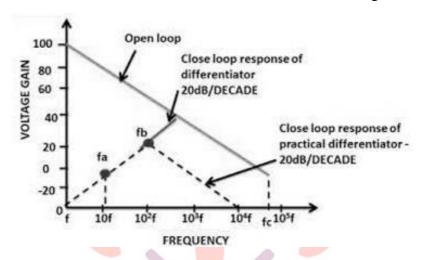

#### **Frequency Response of Differentiator:**

Frequency response is graph relating Gain and Frequency.

Capacitive reactance

$$\mathbf{Xc} = \frac{1}{2\pi fC}$$

As frequency is increases, Xc will decreases and gain will increase.

At low frequency capacitive reactance Xc is high, so gain is low and circuit is stable. But as the frequency is increasing, Xc will decrease which cause the gain to increase. Thus at high frequency input signal, circuit becomes unstable.

So, gain is required to be controlled at high frequency. To control the gain at high frequency, a Resistor  $R_1$  is required to be connected in series with input capacitor  $C_1$  in practical Differentiator circuit. Also a feedback resister  $R_f$  is to be connected in parallel with  $C_f$ . Frequency response of Ideal/Basic differentiator and practical differentiator circuit is as shown in figure.

Frequency Response of Basic & Practical Differentiator

PRACTICAL DIFFERENTIATOR CIRCUIT:

### Practical Differentiator circuit DESIGN:

The frequency at which the gain is 0 dB (Unity) is given by equation

$$f_a = \frac{1}{2\Pi R_f C_1}$$

Frequency at which gain starts decreases is called gain limiting frequency and is given by equation

$$f_b = \frac{1}{2\Pi R_1 C_1}$$

Also gain is controlled by Cf and Rf. Hence gain limiting frequency can be given by equation.

Generally

$$f_b = 20 f_a$$

$$f_b = \frac{1}{2\Pi R_f C_f}$$

Now selecting standard value of capacitor  $C_1$  we can determine the value of  $C_f$ ,  $R_1$  and  $R_f$  using equation of  $\mathbf{f_a}$  and  $\mathbf{f_b}$  to design differentiator of particular frequency range.

#### **INPUT & OUTPUT WAVE FORMS: -**

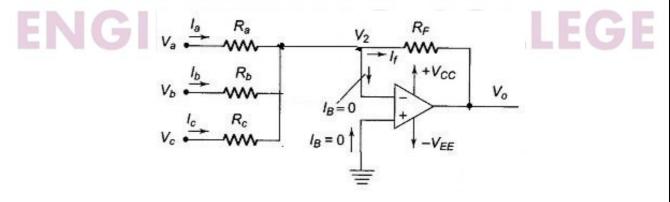

Explain Summing, Scaling and Averaging amplifier using Op. Amp.

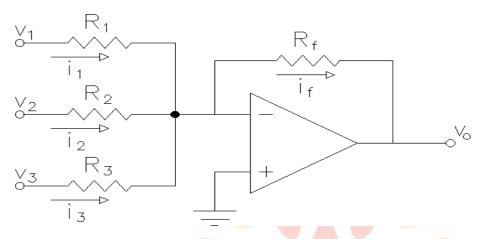

Figure shows an Summing Amplifier Circuit in inverting configuration with three inputs  $V_a$ ,  $V_b$ ,  $V_c$ . Depending on the relation between  $R_a$ ,  $R_b$ ,  $R_c$  and  $R_F$ , the circuit can be used as a Summing amplifier, Scaling amplifier or Average amplifier.

Using Kirchoff's circuit equation, we have  $l_a + l_b + l_c = I_B + I_f$ . But  $I_B \equiv 0$  and  $V_1 \equiv V_2 \equiv 0$  (Virtual ground)

Therefore,

$$I_{a} + I_{b} + I_{c} = I_{f}$$

$$\frac{V_{a} - V_{2}}{R_{a}} + \frac{V_{b} - V_{2}}{R_{b}} + \frac{V_{c} - V_{2}}{R_{c}} = \frac{V_{2} - V_{o}}{R_{f}}$$

--- (2)

As  $V_2$  is virtual ground,  $V_2 = 0$ . Hence equation (2) is

$$\frac{\underline{V}_a}{R_a} + \frac{\underline{V}_b}{R_b} + \frac{\underline{V}_c}{R_c} = \frac{\underline{\mathcal{I}}_o}{R_f} \qquad ---- (3)$$

So,

$$\mathbf{V}_o = -\left[\frac{R_f V_a}{R_a} + \frac{R_f V_b}{R_b} + \frac{R_f V_c}{R_c}\right] \qquad ---- (4)$$

(i) Summing Amplifier:

In equation (4) if  $\mathbf{R}_a = \mathbf{R}_b = \mathbf{R}_c = \mathbf{R}_f = \mathbf{R}$  then equation (4) is

$$V_o = -[V_a + V_b + V_c]$$

---- (5)

Thus circuit will behaves as Summing Amplifier which gives output that is sum of allthe inputs. It is also called *Adder circuit*

(ii) Scaling Amplifier:

In equation (4) if  $\mathbf{R}_a \neq \mathbf{R}_b \neq \mathbf{R}_c \neq \mathbf{R}_f$  then equation (4) is

$$V_o = -\left[\frac{R_f V_a}{R_a} + \frac{R_f V_b}{R_b} + \frac{R_f V_c}{R_c}\right] \qquad ---- (6)$$

Thus circuit will behaves as Scaling Amplifier in which every input is amplified by different scale/weight. Gain of every input is different.

(iii) Averaging Amplifier:

In equation (4) if  $\mathbf{R}_a = \mathbf{R}_b = \mathbf{R}_c = \mathbf{R}$  and  $\mathbf{R} = 3\mathbf{R}_f$  then equation (4) is

$$V_o = -\frac{R_f}{R} [V_a + V_b + V_c] \qquad ---- (7)$$

and

$$V_o = -\left[\begin{array}{c} \underline{V_a + V_b + V} \\ 3 \end{array}\right] \qquad ---- (8)$$

Thus circuit will behaves as Average Amplifier in which output is the average of three inputs..

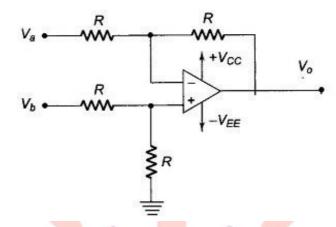

#### Explain Subtractor circuit using Op. Amp.

A subtractor circuit using a basic differential amplifier is as shown in figure.

By selecting the appropriate values for the external resistance, the input signal can be called to the desired value.

As shown in figure, all values of the external resistance are equal, and the gain of theamplifier is unity.

Therefore, the output voltage of differential amplifier with unity gain. As we know

that output voltage in differential amplifier is

$$\mathbf{V_o} = -\frac{R_f}{R_1} \left[ \mathbf{V_a} - \mathbf{V_b} \right]$$

But in above circuit  $R_f = R_1 = R_2 = R_3 = R$

Hence,

$$V_o = -[V_a - V_b] \qquad --- (1$$

#### Explain Subtractor circuit using Op. Amp.

A subtractor circuit using a basic differential amplifier is as shown in figure.

By selecting the appropriate values for the external resistance, the input signal can be called to the desired value.

As shown in figure, all values of the external resistance are equal, and the gain of theamplifier is unity.

Therefore, the output voltage of differential amplifier with unity gain. As we know that output voltage in differential amplifier is

$$\mathbf{V_o} = -\frac{R_f}{R_1} \left[ \mathbf{V}_a - \mathbf{V}_b \right]$$

But in above circuit  $R_f = R_1 = R_2 = R_3 = R$

Hence,

$$V_o = - [V_a - V_b]$$

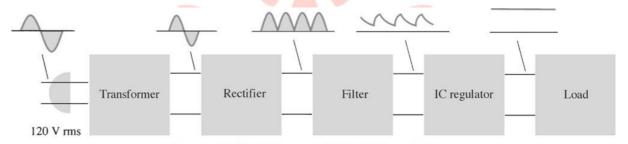

### Explain IC Voltage regulators in detail. OR

Explain three terminal voltage regulators in detail.

A Voltage Regulator is a device or a circuit that is responsible for providing a steady DC Voltage to an electronic load. IC Voltage Regulator uses integrated circuits for voltage regulation.

Block diagram of a power supply which uses IC regulator is as shown in figure

your roots to success...

### Advantages of IC voltages regulators:

- (1) The IC voltage regulator is conveniently used for local regulation.

- (2) The IC voltage regulator is easy to use.

- (3) It is most efficient and reliable.

- (4) The IC voltage regulator is versatile.

- (5) It is very cheap due to mass production and easily available.

- (6) It is compact in size, rugged and light in weight.

- (7) The power supply design becomes easy and quick.

- (8) It is easily manufactured with features like built in protection, programmable output, current or voltage boosting, internal protections such as thermal shutdown, floating operation to facilitate higher output voltage etc.

- (9) It has fast transient response.

### ENGINEERING COLLEGE

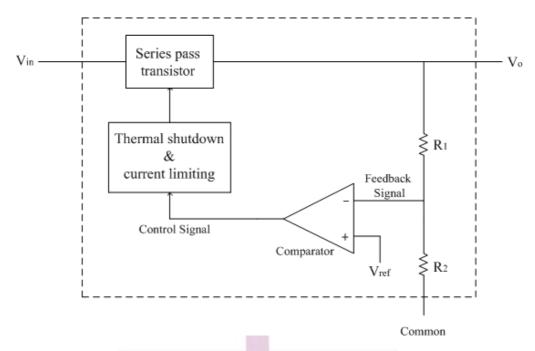

# IC voltage regulators/Three terminal regulator/3-T regulars:

Regulation/regulator circuits in integrated circuit form are most widely used. They are treated as a single device with associated components. These are generally three terminal devices that provide a positive or negative output.

IC regulators contain the circuitry for:

- reference source

- comparator amplifier

- control device

- overload protection

The following figure shows the block diagram of three terminal IC regulato

your roots to success...

# NARSIMHA REDDY ENGINEERING COLLEGE

It has three terminals.

- (1) Input voltage (V<sub>in</sub>)

- (2) Output voltage (V<sub>o</sub>)

- (3) Common terminal (Ground).

Several types of both linear (series and shunt) and switching regulators are available in integrated circuit (IC) form.

Generally, the linear regulators are three-terminal devices that provides either positive or negative output voltages that can be either fixed or adjustable

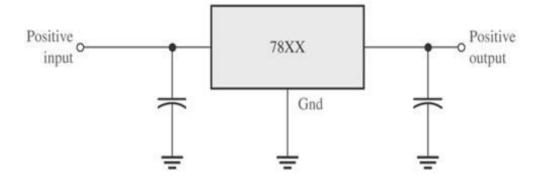

## Fixed voltage regulator:

The fixed voltage regulator has an unregulated dc input voltage  $V_i$  applied to one input terminal, a regulated output dc voltage  $V_o$  from a second terminal, and the third terminal connected to ground.

Fixed-Positive Voltage Regulator

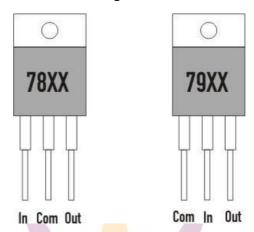

The series 78XX regulators are the three-terminal devices that provide a fixed positive output voltage.

Some of the fixed positive regulator in 78XX series are given in table.

| IC Part | Output Voltage (V) | $Minimum \ V_i \left( V \right)$ |

|---------|--------------------|----------------------------------|

| 7805    | +5                 | +7.3                             |

| 7806    | +6                 | +8.3                             |

| 7808    | +8                 | +10.5                            |

| 7810    | +10                | +12.5                            |

| 7812    | +12                | +14.5                            |

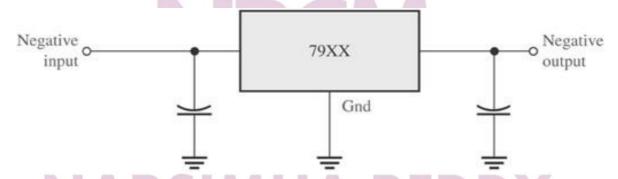

#### Fixed-Negative Voltage Regulator:

The series 79XX regulators are the three-terminal IC regulators that provide a fixednegative output voltage.

This series has the same features and characteristics as the series 78XX regulators except the pin numbers are different.

Some of the fixed negative regulator in 79XX series are given in table.

| IC Part | Output Voltage (V) | Minimum V <sub>i</sub> (V) |

|---------|--------------------|----------------------------|

| 7905    | - 5                | - 7.3                      |

| 7906    | - 6                | - 8.3                      |

| 7908    | - 8                | - 10.5                     |

| 7910    | - 10               | - 12.5                     |

| 7912    | - 12               | - 14.5                     |

Pin configuration of 78XX and 79XX series regulator

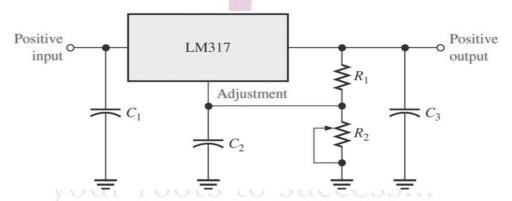

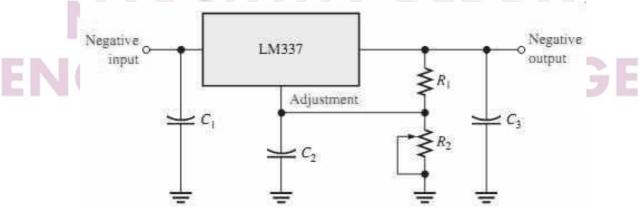

## Adjustable-Voltage Regulator:

Voltage regulators are also available in circuit configurations that allow to set the output voltage to a desired regulated value.

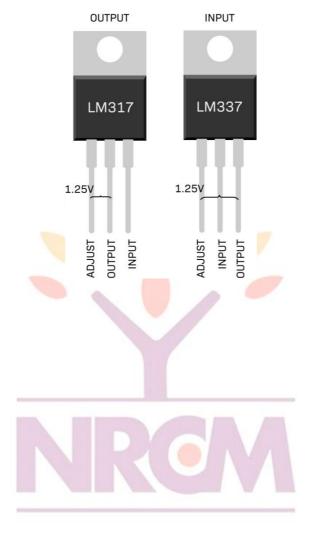

The LM317 is an example of an positive adjustable-voltage regulator, can be operated over the range of voltage from 1.2 to 37 V.

The three terminals are V<sub>in</sub>, V<sub>out</sub>, and Adjustment(adj).

The LM337 series of voltage regulators are a complement of LM317 series. They are negative adjustable voltage regulators. These negative voltage regulators are available in the same voltage and current options as the positive adjustable voltage regulator LM317

Pin configuration of LM317 and LM337 adjustable regulators

your roots to success...

# NARSIMHA REDDY ENGINEERING COLLEGE

#### What is Comparator? Explain basic comparator circuit. OR

What is Comparator? Draw the circuit for Inverting and Non-inverting comparator using Op. Amp. and explain it with necessary waveform.

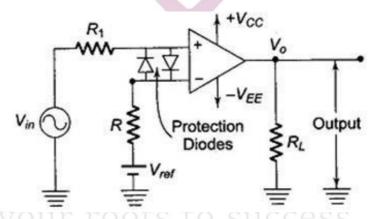

The Op Amp comparator is a circuit with two inputs and a single output. The two inputs can be compared with each other, i.e. one of them can be considered a reference terminal.

When Op. Amp. is used without feedback (open loop configuration), the amplifier output is usually in one of its saturated states.

When the non-inverting input is higher or greater than the inverting input voltage, the output of the comparator is high ( $+V_{sat}$ ) and when the non-inverting voltage is less than the inverting voltage then output of the Comparator is low ( $-V_{sat}$ ).

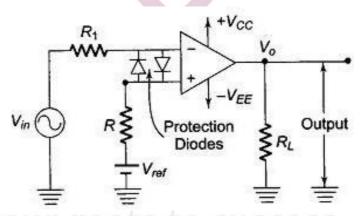

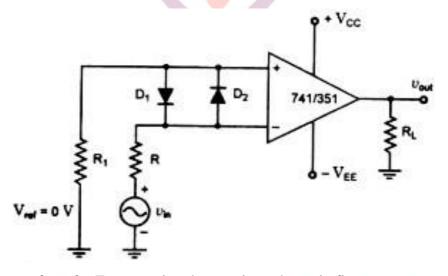

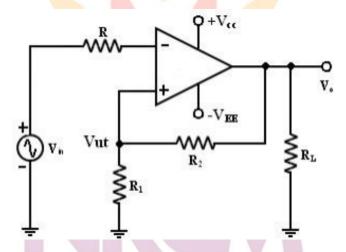

#### **Non-inverting Comparator:**

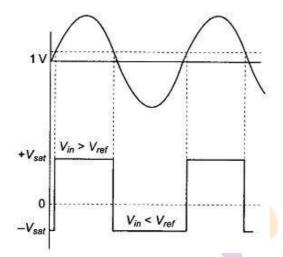

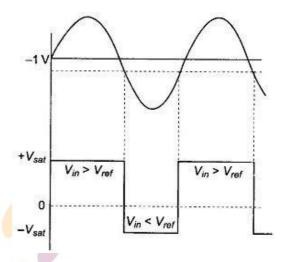

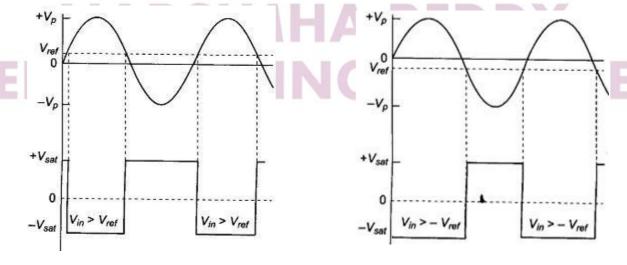

The Op. Amp. Comparator circuit shown in figure, consists of a fixed reference voltage ( $V_{ref}$ ) applied to the inverting input terminal and a sinusoidal signal  $V_{in}$  applied to the non-inverting terminal.

As discussed earlier, when  $V_{in}$  is greater than  $V_{ref}$  the output voltage goes to positive saturation, i.e.  $V_{out} = + V_{sat} = + V_{cc}$  and when  $V_{in}$  is less than  $V_{ref}$ , the output goes to negative saturation, i.e.  $V_{out} = -V_{sat} = -V_{EE}$ .

Hence the output changes from one saturation level to another. Since the sinusoidal input is applying to the non-inverting terminal, this circuit is called the non-inverting comparator.

Diodes  $D_1$  and  $D_2$ , shown in figure are used to protect the Op. Amp. from damage due to excessive input voltage  $(V_{in})$ . The difference input voltage  $(V_{id})$  of the Op. Amp. is clamped to either + 0.7 V or - 0.7 V because of the diodes  $D_1$  and  $D_2$ . Hence the diodes are called clamping diodes.

Necessary input and output waveforms are also shown in figure, in case of  $V_{ref}$  is positive as well as negative.

When V<sub>ref</sub> is Positive

When V<sub>ref</sub> is Negative

#### **Inverting Comparator:**

Inverting comparator can also be obtained by applying the sinusoidal input to theinverting terminal and reference voltage to non-inverting terminal.

Necessary input and output waveforms are also shown in figure, in case of  $V_{\text{ref}}$  is positive as well as negative for inverting comparator.

When V<sub>ref</sub> is Positive

When V<sub>ref</sub> is Negative

#### Characteristics and Application of Comparator

#### **Characteristics:**

Three important characteristics of comparator are

- (i) Speed of operation

- (ii) Accuracy

- (iii) Compatibility of output

#### **Applications**

- (i) Signal generation & transmission

- (ii) Automatic control & measurement

- (iii) A/D converter

- (iv) Voltage level detector

- (v) Window detector/comparator

- (vi) V to F converter

- (vii) Switching regulator

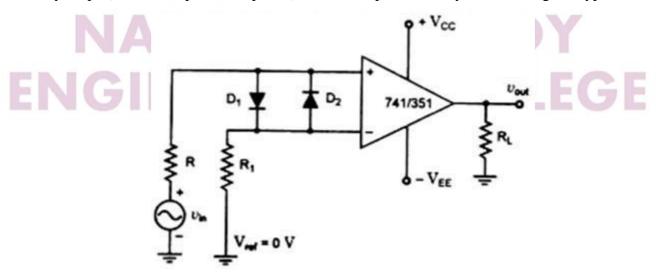

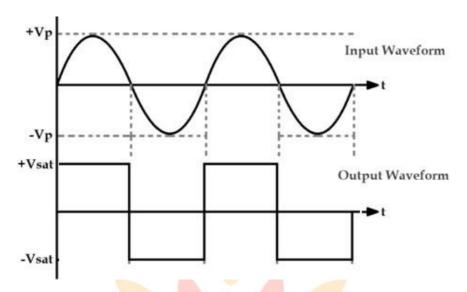

#### **Explain Zero Crossing Detector**•

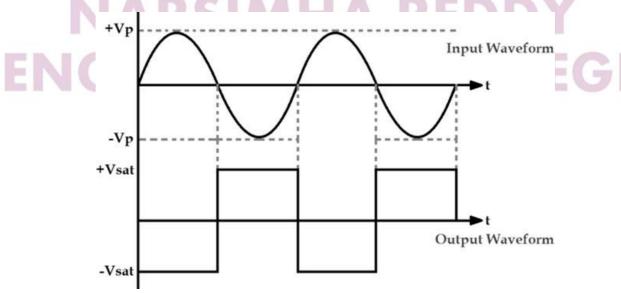

The zero crossing detector circuit in figure is seen to be simply an operational amplifier with the inverting input grounded and the signal applied to the non inverting input.

When the input is above ground level the output is saturated at its positive maximum, and when the input is below ground the output is at its negative maximum level.

This is illustrated by the input and output waveforms which show that the output voltage changes from one extreme to the other each time the input voltage crosses zero. The input waveform could have any shape (sinusoidal, pulse, ramp, etc.), and the output will always be a rectangular-type wave.

Input and output waveform for Zero crossing detector is as shown in figure

If the op-amp non-inverting input is grounded and the signal is applied to the inverting input then output is negative when the input is above ground, and vice versa. Because of the waveform inversion, this circuit is often termed an **inverter**

Input and output waveform for Zero crossing detector is as shown in figure.

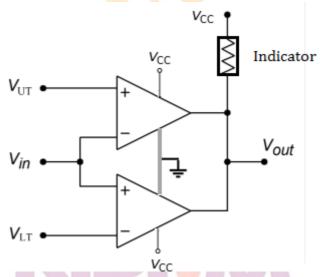

#### **Explain Window Detector/Window comparator circuit**

## A window detector circuit, also called window comparator circuit or dual edge limit detector circuits.

It is used to determine whether an unknown input is between two precise reference threshold voltages. It employs two comparators to detect over-voltage or under- voltage.

Each single comparator detects the common input voltage against one of two reference voltages, normally upper threshold and lower threshold. Outputs detect whether the input is in the range of the so-called "window" between upper and lower threshold reference voltage.

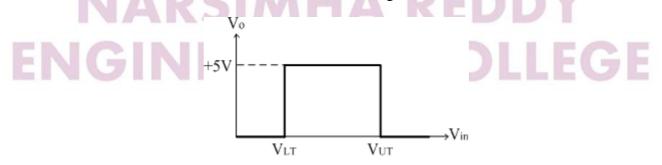

For any value of input voltage  $V_{in} > V_{LT}$  and  $V_{in} < V_{UT}$ , both comparator's output is high, hence

output voltage is High.

But for any value of input voltage  $V_{in} < V_{LT}$  lower comparator generates output low and upper comparator generates output high, so output voltage  $V_{out}$  is low. In the same way for any value of  $V_{in} > V_{UT}$ , output of lower comparator is high but output of upper comparator is low, so output voltage  $V_{out}$  is low.

Hence for any value of  $V_{in} < V_{LT}$  and  $V_{in} > V_{UT}$ , output voltage  $V_{out}$  is Low as shown in graph.

Transfer characteristic of window detector is as shown in figure.

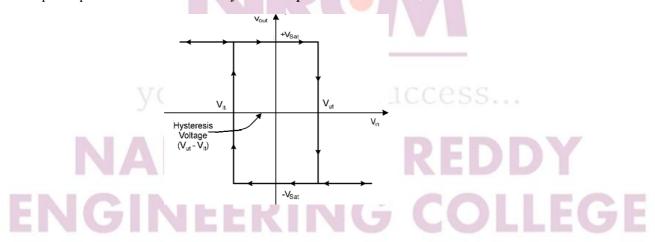

#### **Explain Schmitt Trigger circuit. OR**

## Draw circuit for Inverting Schmitt Trigger. Explain it with necessary equation and also draw Hysteresis loop,

Schmitt trigger is a comparator circuit implemented by applying positive feedback to the non inverting input of a comparator or differential amplifier. It is an active circuit which converts an analog input signal to a digital output signal. The circuit is named a "trigger" because the output retains its value until the input changes sufficiently to trigger a change.

In Inverting configuration, when the input is higher than a certain chosen threshold (Upper Threshold), the output is Low. When the input is lower chosen threshold (Lower Threshold), the output is High, and when the input is between the two levels, the output retains its value. This dual threshold action is called hysteresis.

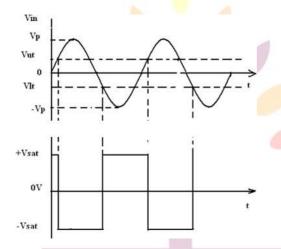

A Schmitt Trigger is a circuit which converts an irregular shaped waveform to a square wave or pulse. This circuit is also called as a squaring circuit. A Schmitt trigger circuit is as shown in figure.

The input voltage  $V_{in}$  triggers (changes the state of) output  $V_{out}$  every time it exceeds certain voltage levels called upper threshold  $V_{ut}$  and lower threshold voltage  $V_{lt}$  as shown in figure.

These threshold voltages can be obtained by using the voltage divider  $R_1$  and  $R_2$ , where the voltage across  $R_1$  is fed back to the (+) input. The voltage across  $R_1$  is a variable reference threshold voltage that depends on the value and the polarity of the output voltage. When  $V_{out} = +V_{sat}$ , the voltage across  $R_1$  is called the upper threshold voltage,  $V_{ut}$ .

$$V_{ut} = \frac{R_1}{R_1 + R_2} \times (+V_{sat}) \qquad (1)$$

On the other hand, when Vout = -Vsat, the voltage across R1 is referred to as lowerthreshold voltage, Vlt.

$$V_{lt} = \frac{R_1}{R_1 + R_2} \times (-V_{sat}) \qquad \dots \qquad (2)$$

The hysteresis voltage is, equal to the difference between Vut and Vlt. Therefore,

$$V_{hy} = V_{ut} - V_{lt}$$

$$V_{hy} = \frac{R_1}{R_1 + R_2} \times [+V_{sat} - (-V_{sat})] \qquad (3)$$

Input and output waveform for Schmitt trigger circuit is as shown in figure.

A graph of output voltage  $(V_0)$  versus input voltage  $(V_i)$  can be plotted for an invertingSchmitt Trigger Circuit Diagram, as shown in figure.

This input/output characteristic is called *Hysteresis loop*.

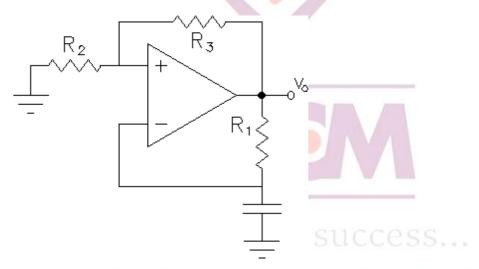

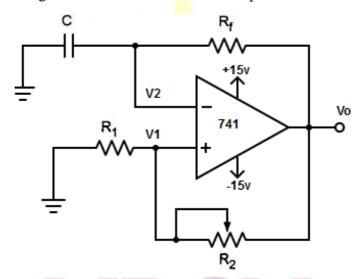

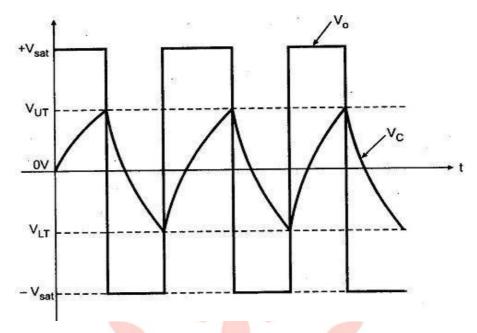

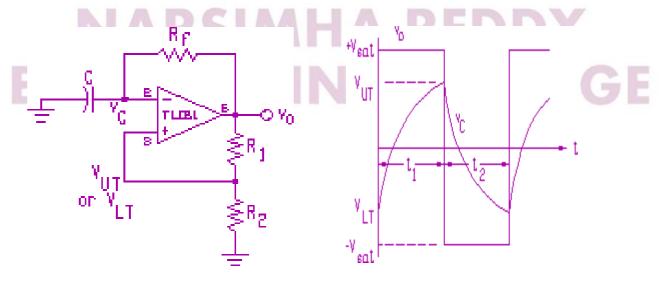

#### Explain Square wave generator circuit using Op. Amp.

The Square Wave Generator using Op Amp. means the Astable Multivibrator circuit using op-amp. It generates the square wave of required frequency. The figure shows the square wave generator using Op. Amp.

The circuit has a time dependent elements such as resistance and capacitor to set the frequency of oscillation.

As shown in the figure resistors  $R_1$  and  $R_2$  form an positive feedback.

When  $V_0$  is at  $+V_{sat}$ , the feedback voltage  $V_1$  is called the upper threshold voltage  $V_{UT}$  and is given as

$$V_{1} = V_{UT} = \frac{+V_{Sat} R_{1}}{R_{1} + R_{2}}$$

---- (1)

When  $V_0$  is at - $V_{\text{sat}}$ , the feedback voltage  $V_1$  is called the lower threshold voltage  $V_{\text{LT}}$  and is given as

$$V_1 = V_{LT} = \frac{-V_{Sat} R_1}{R_1 + R_2} - \cdots (2)$$

When power is turn ON, output is assumed to be  $+V_{sat}$  because of positive feedback. With  $V_o = +V_{sat}$  we have  $V_1 = V_{UT}$  and capacitor starts charging towards  $+V_{sat}$  through the feedback path provided by the resistor  $R_f$  at the inverting input.

This is illustrated in figure. As long as the capacitor voltage  $V_c$  is less than  $V_{\text{UT}}$ , the output voltage remains at  $+V_{\text{sat}}$

As soon as  $V_c$  charges to a value slightly greater than  $V_{UT}$ , the inverting (-) input becomes higher than non inverting (+) input. This switches the output voltage from +Vsat to -Vsat and we have  $V_1 = V_{LT}$  which is negative with respect to ground. As  $V_o$

switches to  $-V_{sat}$ , capacitor starts discharging via  $\mathbf{R_f}$ , as shown in the figure.

The current I discharges capacitor to 0 V and recharges capacitor to  $V_{LT}$ . When  $V_c$  becomes slightly more negative than the feedback voltage  $V_{LT}$ , the non inverting (+) input is higher than inverting (-) input. This switches the output voltage from -Vsat to

+Vsat and we have  $V_1 = V_{UT}$  again which is positive with respect to ground..

As a result, capacitor now has a initial charge equal to  $V_{LT}$ . The capacitor will discharge from  $V_{LT}$  to O Volt and then recharge to  $V_{UT}$ , and the process is repeating. Once the, initial cycle is completed, the waveforms become periodic, as shown in the figure.

The frequency of oscillation is determined by the time it takes the capacitor to charge from  $V_{UT}$  to  $V_{LT}$  and vice versa.

Time period of output waveform is given by equation

$$T = 2RC \ln \left[ \frac{2R_1 + R_2}{R_2} \right] \qquad ---- (3)$$

Hence frequency of output waveform is given by equation

$$f = \frac{1}{T} = \frac{1}{2RC \ln \left[\frac{2R1 + R2}{R_2}\right]} \qquad --- (4)$$

in equation (4) if  $R_2 = 1.16R_1$  then

$$f = \frac{1}{2RC} \qquad ---- (5)$$

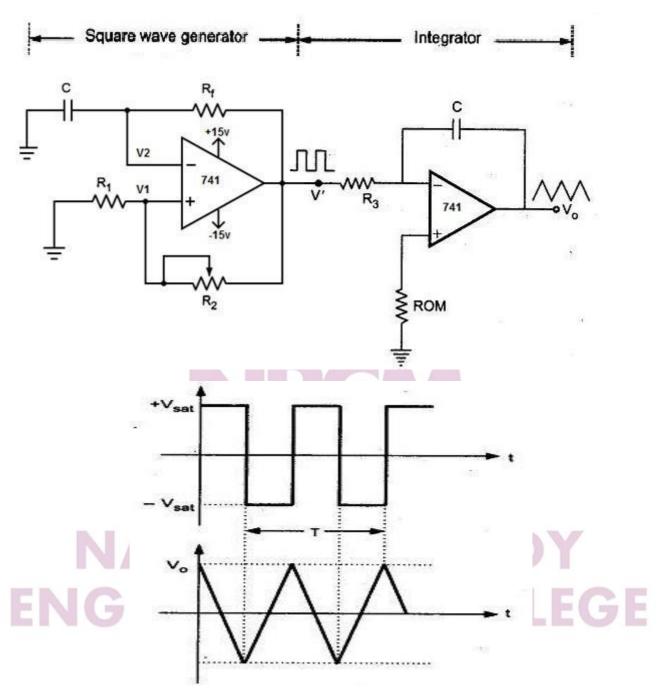

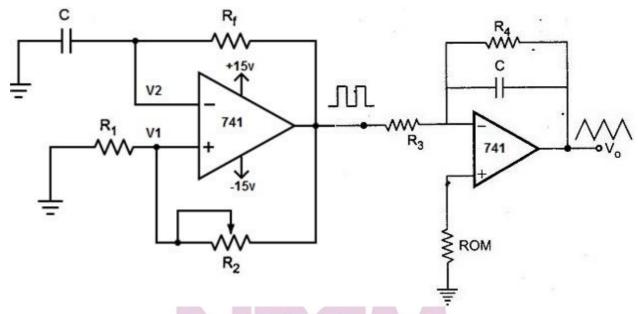

#### Explain Triangular wave generator circuit using Op. Amp.

As we know that output of integrator is a Triangular Wave, if its input is a square wave. This means that a Triangular Wave Generator Using Op Amp can be formed by simply connecting an integrator to the square wave generator as shown in the figure.

Basically, triangular wave is generated by alternatively charging and discharging a capacitor with a constant current. This is achieved by connecting integrator circuit at the output of square wave generator. Assume that V' is high at  $+V_{sat}$ . This forces a constant current ( $+V_{sat}/R_3$ ) through C (left to right) to drive  $V_o$  negative linearly. When V' is low at  $-V_{sat}$ , it forces a constant current ( $-V_{sat}/R_3$ ) through C (right to left) to drive

V<sub>o</sub> positive, linearly. The frequency of the triangular wave is same as that of square wave.

This is illustrated in figure. Although the amplitude of the square wave is constant ( $\pm$  V<sub>sat</sub>), the amplitude of the triangular wave decreases with an increase in its frequency, and vice versa. This is because the reactance of capacitor decreases at high frequencies and increases at low frequencies.

In practical circuits, resistance  $R_4$  is connected across C to avoid the saturation problem at low frequencies as in the case of practical integrator as shown in the figure.

Time period of output waveform is given by equation

$$T = 2RC \ln \left[ \frac{2R_1 + R_2}{R_2} \right] \qquad ---- (1)$$

Hence frequency of output waveform is given by equation

$$f = \frac{1}{T} = \frac{1}{2RC \ln \left[\frac{2R1 + R2}{R_2}\right]} --- (2)$$

in equation (4) if  $R_2 = 1.16R_1$  then

$$f = \frac{1}{2RC} \qquad ---- (3)$$

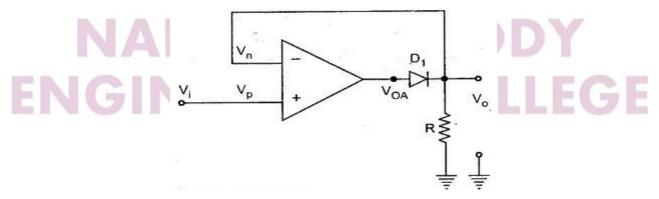

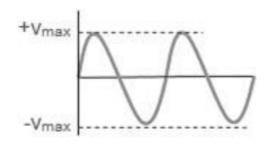

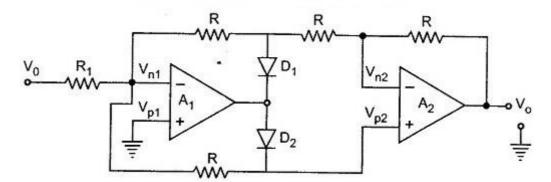

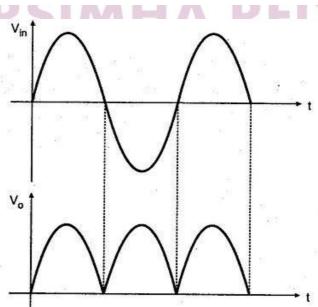

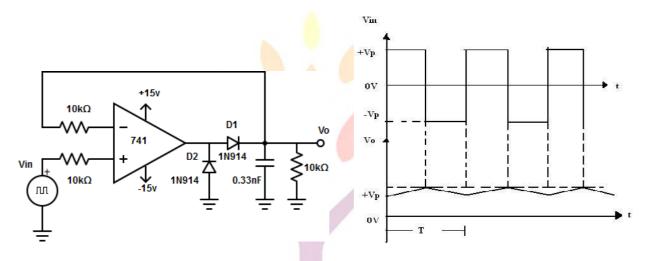

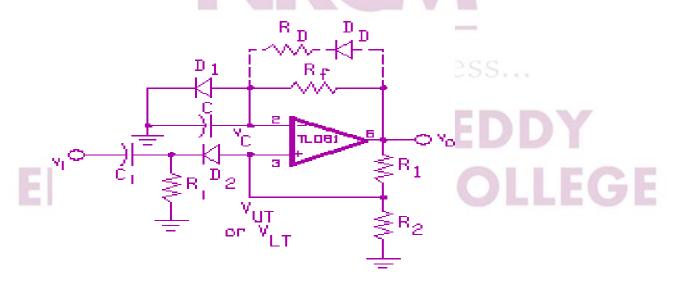

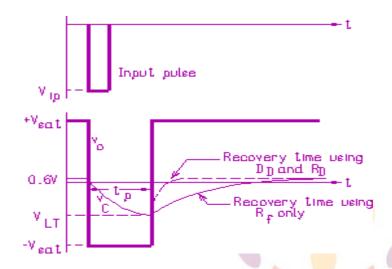

# Explain precision Half wave rectifier circuit using Op. Amp.

Rectifier circuits can be also implemented with a diode/diodes (half wave rectifier or full wave rectifier).

The major limitations of these Rectifiers circuits is that they cannot rectify voltages below  $V_D = 0.7$  V, the cut-in voltage of the diode. Hence

$$V_o = V_i - V_{D(ON)}$$

for  $V_i \ge V_{D(ON)}$

$V_o = 0 \text{ V}$  for  $V_i \le V_{D(ON)}$

Due to this, output of the conventional rectifier is distorted.

To achieve *Precision Rectifiers* we need a circuit that keeps  $V_o$  equal to  $V_i$  for  $V_i > O$  V. This can be achieved by using Op. Amp. along with the diodes and these circuits are called *Precision Rectifiers*. These are used to precisely rectify voltages having amplitudes less than 0.7 V.

## **Precision Half Wave Rectifiers**

There are two types of precision half wave rectifiers available,

- (i) Non inverting half wave rectifier

- (ii) Inverting half wave rectifier

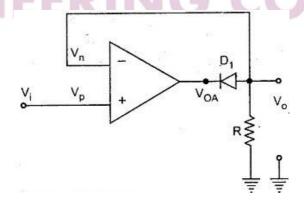

## Non inverting Half Wave Rectifier:

Figure shows precision half wave rectifier. It consists of non inverting amplifier with diode  $D_1$  in the feedback loop of an Op. Amp

The analysis of this circuit can be done considering two distinct cases for  $V_{\rm i} > 0 \ V$

and  $V_i < 0 V$

CASE 1:

$$V_i > OV$$

:

For closed loop Op. Amp.  $V_p = V_n$ , due to virtual ground.

When  $V_i > 0$ , Op. Amp. tries to keep  $V_o = V_n = V_p = V_i$  (Voltage follower circuit) and it does this because forward biasing diode provides closed loop feedback path. The voltage drop across forward bias diode  $V_D = 0.7 \ V$ .

To accommodate the voltage drop across diode the Op. Amp. swings about 0.7 Vhigher than  $V_{\text{o}}$ , as shown in the figure.

#### CASE $2: V_i < OV:$

When  $V_i < O V$ , diode  $D_1$  is reverse biased and the Op. Amp. is working in the open loop, as shown in the figure.

Therefore, Op. Amp. is no longer capable of keeping  $V_n = V_p$ . With no current through resistance R we have  $V_0 = 0$ .

Since

$$V_n = V_0 = 0$$

and  $V_p = V_i < 0$

The input and output waveforms are shown in figure

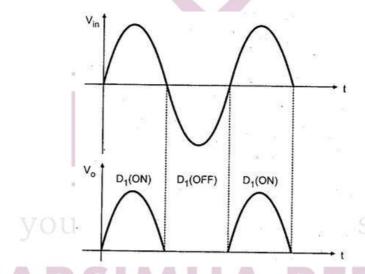

### **Inverting Half Wave Rectifier**

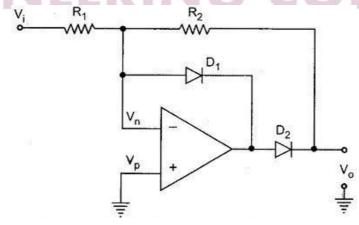

Figure shows another popular circuit, inverting half-wave rectifier. It consists of two diodes and two resistors and Op. Amp. is connected in the inverting configuration.

CASE 1:  $V_i > 0$ :

Recalling virtual ground concept we can say that  $V_p = V_n = O V$ .

For  $V_i > 0$ ,  $V_i$  is positive with respect to  $V_n$  and hence current through  $R_1$  flows from left to right. Only one path for this current to flow is through diode  $D_1$ . Hence diode  $D_1$  is forward biased and diode  $D_2$  is reverse biased. As current flow through  $R_2$  is zero,  $V_o = V_n = O V$ .

CASE 2:  $V_i < 0$ :

For  $V_i < 0$ ,  $V_i$  is negative with respect to  $V_n$  and hence current through  $R_1$  flows from right to left. Only one path for this current to flow is through diode  $D_2$  and resistor  $R_2$ , indicating that  $V_0 > V_n$ . Hence diode  $D_1$  is OFF, and diode  $D_2$  is ON. With these diode states, circuit acts like an inverting amplifier and output voltage is given as

$$V_o = -\frac{R_2}{R_1} V_i$$

for  $V_i < 0 V$

If  $R_1$  and  $R_2$  are made equal, then we can write  $V_o = -V_i$ The input and output waveforms are shown in figure.

Non inverting Half Wave Rectifier which rectifies negative half cycle:

Input waveform

Output waveform

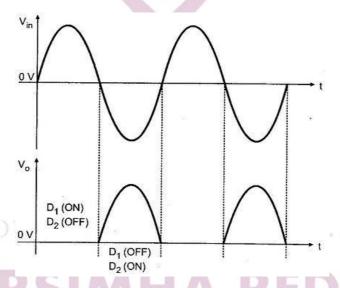

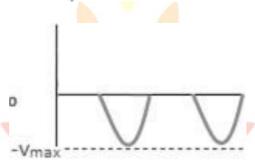

#### **Precision Full Wave Rectifier:**

## Explain Peak Detector circuit using Op. Amp

Square, Triangular, Sawtooth and pulse waves are typical examples of non-sinusoidal waveforms. A conventional ac voltmeter cannot be used to measure these sinusoidal waveforms because it is designed to measure the RMS value of the pure sine wave. One possible solution to this problem is to measure the peak values of the non-sinusoidal waveforms. Peak detector measures the +ve peak value of the square wave input.

During the positive half cycle of V<sub>in</sub>:

The output of the Op. Amp. drives  $D_1$  in Forward bias, Charging capacitor C to the positive peak value  $V_p$  of the input volt  $V_{in}$ .

During the negative half cycle of V<sub>in</sub>:

$D_{\rm l}$  is reverse biased and voltage across C is retained. The only discharge path for C is through  $R_{\rm L}.$

For proper operation of the circuit, the charging time constant  $(CR_d)$  and discharging time constant  $(CR_L)$  must satisfy the following condition.

$$CR_d <= T/10$$

Where  $R_d$  = Resistance of the forward-biased diode.T = time period of the input waveform.

$$CR_L >= 10T$$

Where  $R_L = Load$  Resistor.

Resistor R is used to protect the op-amp against the excessive discharge currents. Diode  $D_2$  conducts during the –ve half cycle of  $V_{in}$  and prevents the op-amp from goinginto negative saturation.

Negative peak of the input signal can be detected simply by reversing diode  $D_1$  and  $D_2$ .

# ACTIVE FILTERS AND OSCILLATOR

#### **Filter**

Filter is a frequency selective circuit that passes signal of specified Band of frequencies and attenuates the signals of frequencies outside the band

#### Type of Filter

- 1. Passive filters

- 2. Active filters

#### **Passive filters**

Passive filters works well for high frequencies. But at audio frequencies, the inductors become problematic, as they become large, heavy and expensive. For low frequency applications, more number of turns of wire must be used which in turn adds to the series resistance degrading inductor's performance ie, low Q, resulting in high power dissipation

#### **Active filters**

Active filters used op- amp as the active element and resistors and capacitors as passive elements. By enclosing a capacitor in the feed back loop, inductor less active filters can be obtained

MHA RED

RING COLLEGE

#### Some commonly used active filters

- 1. Low pass filter

- 2. High pass filter

- 3. Band pass filter

- 4. Band reject filter

#### **Active Filters**

- Active filters use op-amp(s) and RC components.

- Advantages over passive filters:

- op-amp(s) provide gain and overcome circuit losses

- increase input impedance to minimize circuit loading

- higher output power

- sharp cutoff characteristics can be produced simply and efficiently without bulky inductors

• Single-chip universal filters (e.g. switched-capacitor ones) are available that can be configured for any type of filter or response.

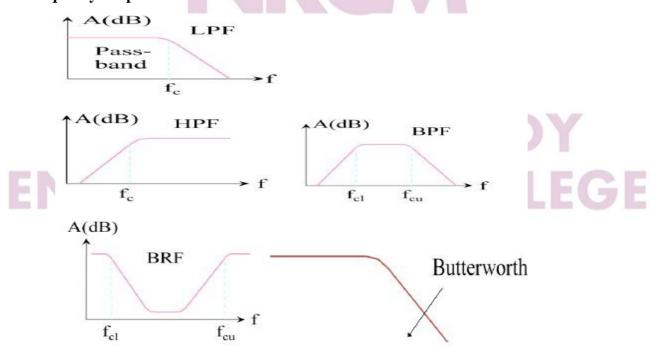

#### **Review of Filter Types & Responses**

- 4 major types of filters: low-pass, high-pass, band pass, and band-reject or band-stop

- 0 dB attenuation in the pass band (usually)

- 3 dB attenuation at the *critical* or *cutoff frequency*, fc (for Butterworth filter)

- Roll-off at 20 dB/dec (or 6 dB/oct) per *pole* outside the passband (# of poles = # of reactive elements). Attenuation at any frequency, f, is

- Bandwidth of a filter:  $BW = f_{cu} f_{cl}$

- Phase shift: 45<sub>o</sub>/pole at f<sub>c</sub>; 90<sub>o</sub>/pole at >> f<sub>c</sub>

- 4 types of filter responses are commonly used:

- Butterworth maximally flat in passband; highly non-linear phase response

with frequency

- Bessel gentle roll-off; linear phase shift with freq.

- Chebyshev steep initial roll-off with ripples in passband

- Cauer (or elliptic) steepest roll-off of the four types but has ripples in the

passband and in the stop band

#### **Frequency Response of Filters**

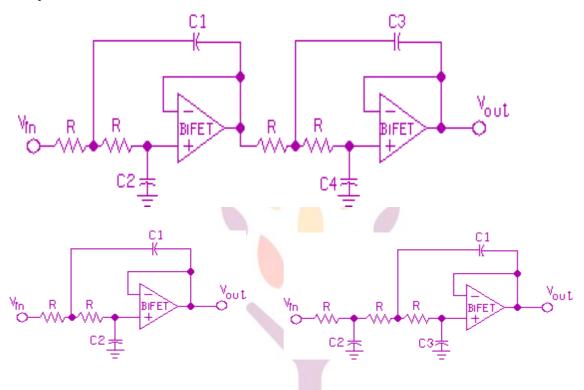

Unity-Gain Low-Pass Filter Circuits

#### **Unity-Gain Low-Pass Filter Circuits**

#### **Design Procedure for Unity-Gain HPF**

- The same procedure as for LP filters is used except for step #3, the normalized C value of 1 F is divided by  $K_f$ . Then pick a desired value for C, such as 0.001 mF to 0.1 mF, to calculate  $K_x$ . (Note that all capacitors have the same value).

- For step #6, multiply all normalized R values (from table) by Kx.

E.g. Design a unity-gain Butterworth HPF with a critical frequency of 1 kHz, and a roll-off of 55 dB/dec. (Ans.: C = 0.01 mF,  $R_1 = 4.49$  kW,  $R_2 = 11.43$  kW,  $R_3 = 78.64$  kW.; pick standard values of 4.3 kW, 11 kW, and 75 kW).

#### **Equal-Component Filter Design**

Design an equal-component LPF with a critical frequency of 3 kHz and a roll-off of 20 dB/oct.

Minimum # of poles = 4

Choose C = 0.01 mF;  $^{\circ} R = 5.3 \text{ kW}$

From table, Av1 = 1.1523, and Av2 = 2.2346.

Choose  $R_{11} = R_{12} = 10 \text{ kW}$ ; then  $R_{F1} = 1.5 \text{ kW}$ , and  $R_{F2} = 12.3 \text{ kW}$ .

Select standard values: 5.1 kW, 1.5 kW, and 12 kW.

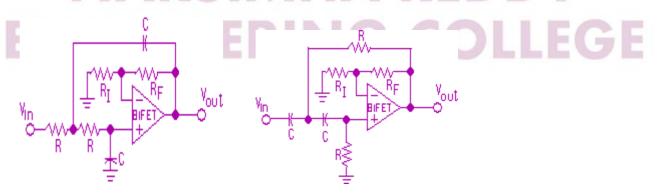

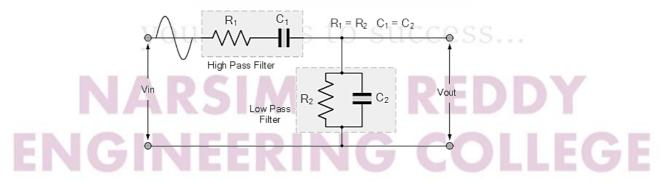

#### **Bandpass and Band-Rejection Filter**

#### A broadband BPF can be obtained by combining a LPF and a HPF

#### **Broadband Band-Reject Filter**

A LPF and a HPF can also be combined to give a broadband BRF

#### Narrow-band Bandpass Filter

#### Narrow-band Band-Reject Filter

Easily obtained by combining the inverting output of a narrow-band BRF and the original signal

The equations for R1, R2, R3, C1, and C2 are the same as before.

$R_I = R_F$  for unity gain and is often chosen to be  $>> R_1$ .

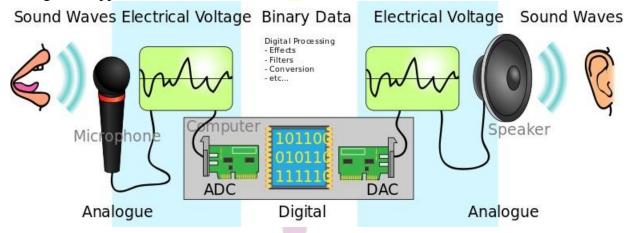

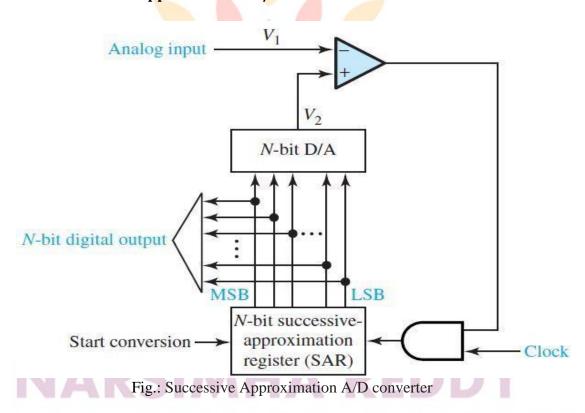

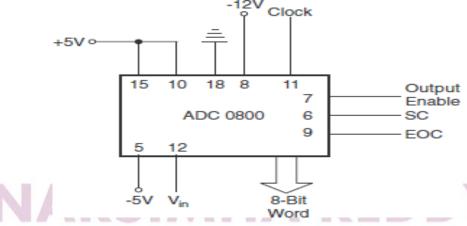

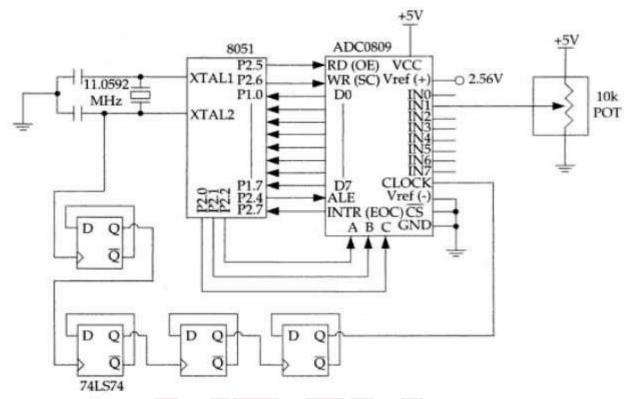

#### **Classification of ADCs**

- 1. Direct type ADC.

- 2. Integrating type ADC

#### **Direct type ADCs**

- 1. Flash (comparator) type converter

- 2. Counter type converter

- 3. Tracking or servo converter.

- 4. Successive approximation type converter

#### **Integrating type converters**

An ADC converter that perform conversion in an indirect manner by first changing the analog I/P signal to a linear function of time or frequency and then to a digital code is known as integrating type A/D converter

#### Sample and hold circuit

A sample and hold circuit is one which samples an input signal and holds on to its last sampled value until the input is sampled again. This circuit is mainly used in digital interfacing, analog to digital systems, and pulse code modulation systems

#### **Dual slope ADC:**

Dual slope conversion is an indirect method for A/D conversion where an analog voltage and a reference voltage are converted into time periods by an integrator, and then measured by a counter. The speed of this conversion is slow but the accuracy is high

Advantages of dual slope ADC are

- 1. It is highly accurate

- 2. Its cost is low

- 3. It is immune to temperature caused variations in R1 and C1

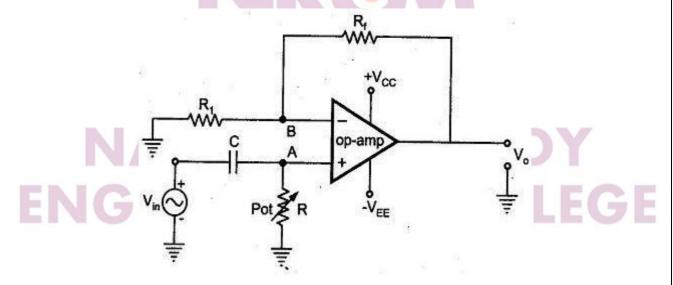

#### Explain RC phase shift Oscillator using Op. Amp,

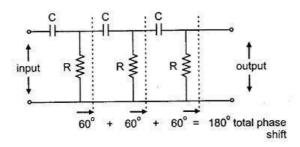

RC Phase Shift Oscillator basically consists of an amplifier and a feedback network consisting of resistors and capacitors arranged in ladder fashion. Hence such an oscillator is also called ladder type RC Phase Shift Oscillator.

RC network is used in feedback path. In oscillator, feedback network must introduce a phase shift of 180° to obtain total phase shift around a loop as 360°. Thus if one RC network produces phase shift of 60° then to produce phase shift of 180° such three RC networks must be connected in cascade.

Hence in RC phase shift oscillator, the feedback network consists of three RC sections each producing a phase shift of 60°, thus total phase shift due to feedback is 180° (3x 60°). Such a feedback network is shown in the figure.

your roots to success...

# NARSIMHA REDDY ENGINEERING COLLEGE

The network is also called the **ladder network.** All the resistance values and all the capacitance values are same, so that for a particular frequency, each section of R and C produces a same phase shift of 60°.

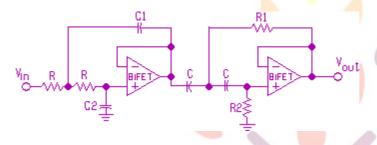

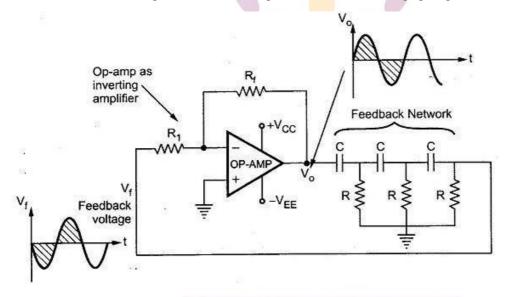

In R-C phase shift oscillator op-amp connected in inverting amplifier mode. Thus it introduces the phase shift of 180° between input and output. The feedback network consists of 3 RC sections each producing 60° phase shift. Hence total phase shift around a close loop is 360°. Such a RC phase shift oscillator using op-amp is shown in the figure.

The output of amplifier is given to feedback network. The Output of feedback network drives the amplifier. The total phase shift around a loop is  $180^{\circ}$  of amplifier and  $180^{\circ}$  due to 3 RC section, thus  $360^{\circ}$ . This satisfies the required condition for positive feedback and circuit works as an oscillator.

The frequency of sustained oscillations generated depends on the values of R and C and is given by,

$$f = \frac{1}{2\pi\sqrt{6}\ R\ C}$$

The frequency is measured in Hz.

At this frequency the gain of the op-amp must be at least 29 to satisfy loop gain  $A\beta = 1$ . Now gain of the op-amp inverting amplifier is given by,

$$|A| \ge \frac{R_f}{R_1} \ge 29$$

for oscillations  $R_f \ge 29 R_1$

Thus circuit will work as an oscillator which will produce a sinusoidal waveform if gain is 29 and total phase shift around a loop is 360°. This satisfies the Barkhausen criterion for the oscillator. These oscillators are used over the audio frequency range i.e. about 20Hz up to 100 kHz.

#### Advantages

- (i) The circuit is simple to design.

- (ii) Can produce output over audio frequency range.

- (iii) Produces sinusoidal output waveform.

- (iv) It is a fixed frequency oscillator.

#### Disadvantages

- (i) phase shift oscillator is fixed frequency oscillator. Frequency cannot be varied.

- (ii) Frequency stability is poor.

#### Explain Wien Bridge Oscillator using Op. Amp,

The Wien Bridge is one of the simplest and best known oscillators and is used extensively in circuits for audio applications.

This is also RC oscillator which uses RC type of feedback network. Wien bridge oscillator uses a **non-inverting amplifier.** So in Wien bridge type there is no phaseshift necessary through the feedback network.

The two arms of the bridge, namely R1, C1 in series and R2, C2 in parallel are called **frequency sensitive arms.** This is because the components of these two arms decide the frequency of the oscillator.

Such a feedback network is called **lead–lag network.**

The resistance R and capacitor C are the components of frequency sensitive arms of thebridge.

Negative feedback path to control gain  $R_f$   $R_1$   $R_1$   $R_1$   $R_1$   $R_1$   $R_2$   $R_2$ Positive feedback path to create oscillations

The resistance Rf and R1 form the part of the feedback path. The gain of non inverting op-amp can be adjusted using the resistance Rf and R1. The gain of op-amp is,

$$A = 1 + \frac{R_f}{R_1}$$

To satisfy Barkhausen criterion that AB=1 it is necessary that the gain of the noninverting op-amp amplifier must be minimum 3.

$$|A| \geq 3 \quad i.e \quad 1 + \frac{R_f}{R_1} \geq 3$$

$$\frac{R_f}{R_1} \geq 2$$

Thus ratio of R<sub>f</sub> and R<sub>1</sub> must be greater than or equal to 2. The frequency of oscillations is given by,

your ro

$$f = \frac{1}{2\pi RC} Hz$$

success.

The feedback is given to the non inverting terminal of op-amp which ensures zerophase shift.

If in a Wien bridge feedback network, two resistances are not equal i.e. they are R1 and R2 while two capacitors are not equal i.e. they are C1 and C2 then the frequency of oscillations is given by,

# ENGINEERING COLLEGE

$$f = \frac{1}{2\pi \sqrt{R_1 R_2 C_1 C_2}}$$

With  $R_1 = R_2 = R$  and  $C_1 = C_2 = C$  we get it as  $1/2\pi$  RC as stated earlier.

Advantages

- (i) It is stable.

- (ii) We can change the frequency very effectively.

- (iii) The perfect sine wave output is possible.

- (iv) It is useful audio frequency range i.e. 20 Hz to 100 kHz. Disadvantages

- (i) The maximum frequency output is limited.

#### **Explain Active Filters**

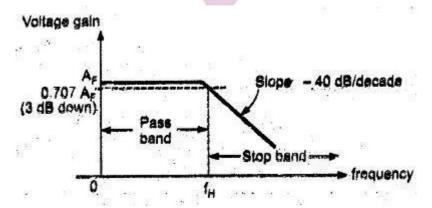

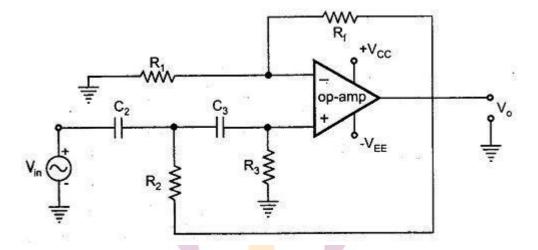

Active Filters is a circuit that is designed to pass a specified band frequencies while attenuating all the signals outside that band. It is a frequency selective circuit.

The filters are basically classified as *active filters* and *passive filters*. The passive filter networks use only passive elements such as resistors, inductors and capacitors. On the other hand, *active filter circuits use the active elements such as op-amps, transistors along with the resistors, inductors and capacitors*. Modern active filters do not use inductors as the inductors are bulky, heavy and nonlinear. The inductors generate the stray magnetic fields. The inductors dissipate considerable amount of power.

#### **Advantages of Active Filters**

- (i) Flexibility in Gain and Frequency Adjustment: The op-amp gain can be easily controlled in closed loop fashion, hence active filter input signal is not attenuated. The passive filters need the attenuation. The active filters can be easily tuned.

- (ii) No Loading Effect: The op-amp has high input impedance and low output impedance. Hence active filter using op-amp does not cause loading of the source or load.

- (iii) Cost: Due to availability of modern ICs, a variety of cheaper op-amps are available. The inductors are absent which makes the modern active filters more economical than passive filters.

The most commonly used filters are:

- 1) Low Pass (LP) filter

- 2) High pass (HP) filter

- 3) Band Pass (BP) filter

**4) Band Reject (BR) filter.** This is also called as Band Stop Filter (BS) or Band Elimination (BE) filter.

#### 5) All Pass filter

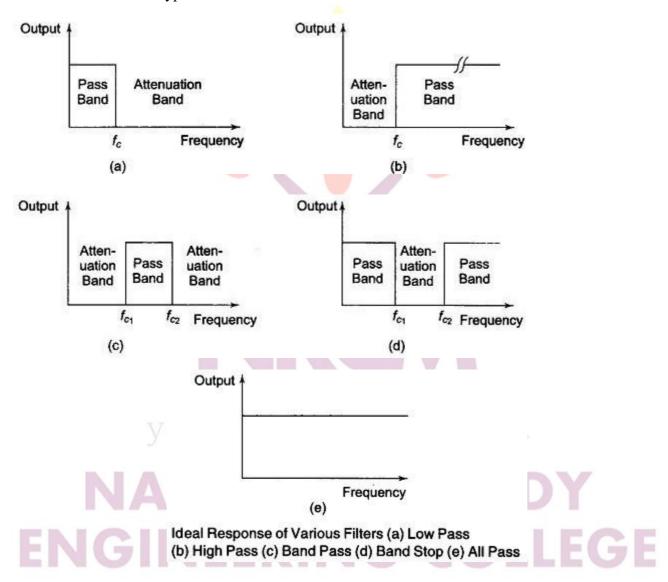

#### Frequency response of Ideal filter:

Each of these filters use op-amp as an active element and resistors and capacitors. Frequency response characteristics of these types of filters are as follow:

#### **Active Filters Types:**

There are basically four useful Active Filters Types.

- 1. Butterworth

- 2. Chebyschev

- 3. Bessel

- 4. Elliptic

#### Frequency response of major practical Active Filters

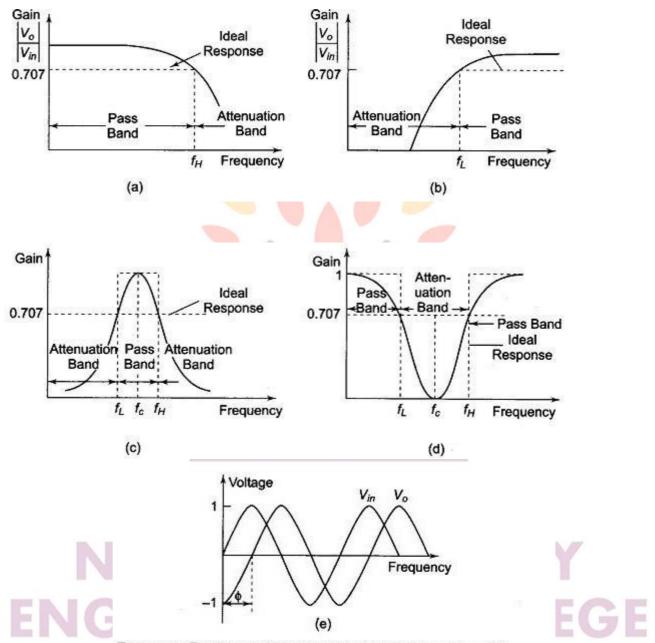

Figure shows the frequency response characteristics of the Active Filters Classification. The ideal response is shown by the dashed lines, while solid lines indicate the *practical filter response*.

Frequency Response of Major Active Filters (a) Low Pass Filter

- (b) High Pass Filter (c) Band Pass Filter (d) Band Stop Filter

- (e) Phase Relation of Input and Output Waveform in an all Pass Filter

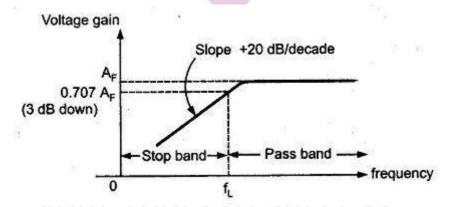

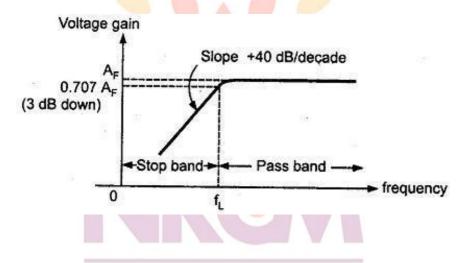

#### First order Law Pass Butterworth Filters

The Butterworth filter has an essentially flat amplitude versus frequency response upto the cutoff frequency.

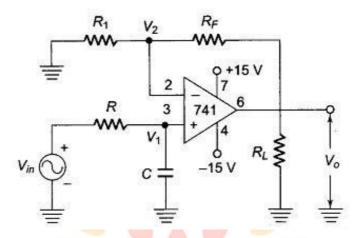

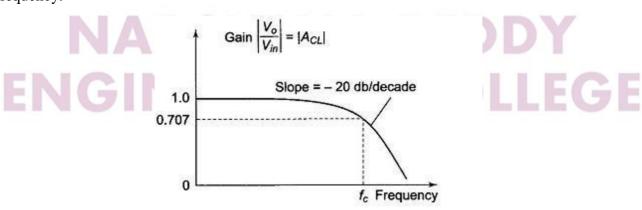

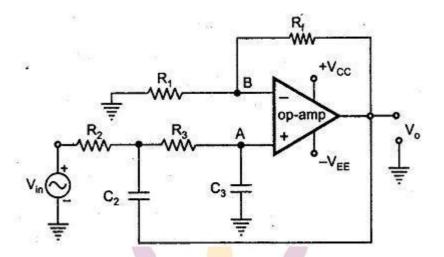

A *first order low pass Butterworth filter* can be obtained from the Basic Low Pass Filter Circuit using an RC filter network.

Figure shows a first order low pass Butterworth filter that uses an RC network for filtering. The op.amp. is used in the non-inverting configuration, which does not loadthe RC network.  $R_1$  and  $R_F$  determine the gain of the filter (in this case unity).

Using the voltage divider rule, the voltage across the capacitor, i.e. at the non-inverting input is

$$V_1 = \frac{-j X_c}{R - j X_c} \times V_{in}$$

, but  $-j X_c = \frac{1}{j2\pi f_C}$

Simplifying, we get

$$V_1 = \frac{V_{in}}{j2\pi f CR + 1}$$

As output voltage

$$V_{o} = \left(1 + \frac{R_{F}}{R_{1}}\right) \times V_{1}$$

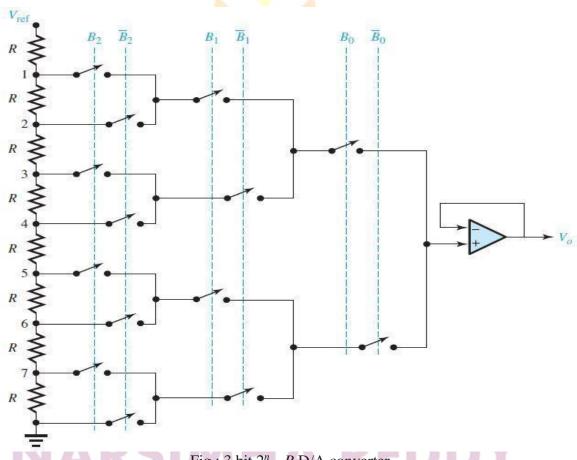

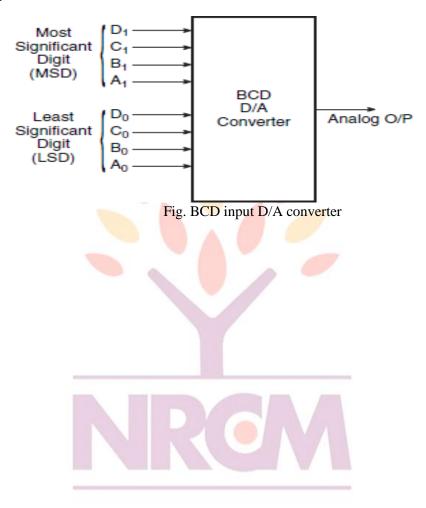

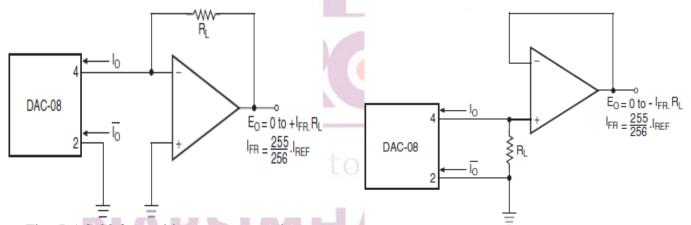

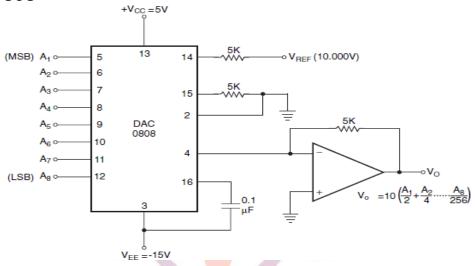

$$V_{o} = \left(1 + \frac{R_{F}}{R_{1}}\right) \times \left(\frac{V_{in}}{1 + j2\pi f CR}\right)$$